Как устроен процессор

Как устроен процессор

Устройство современного процессора компьютера

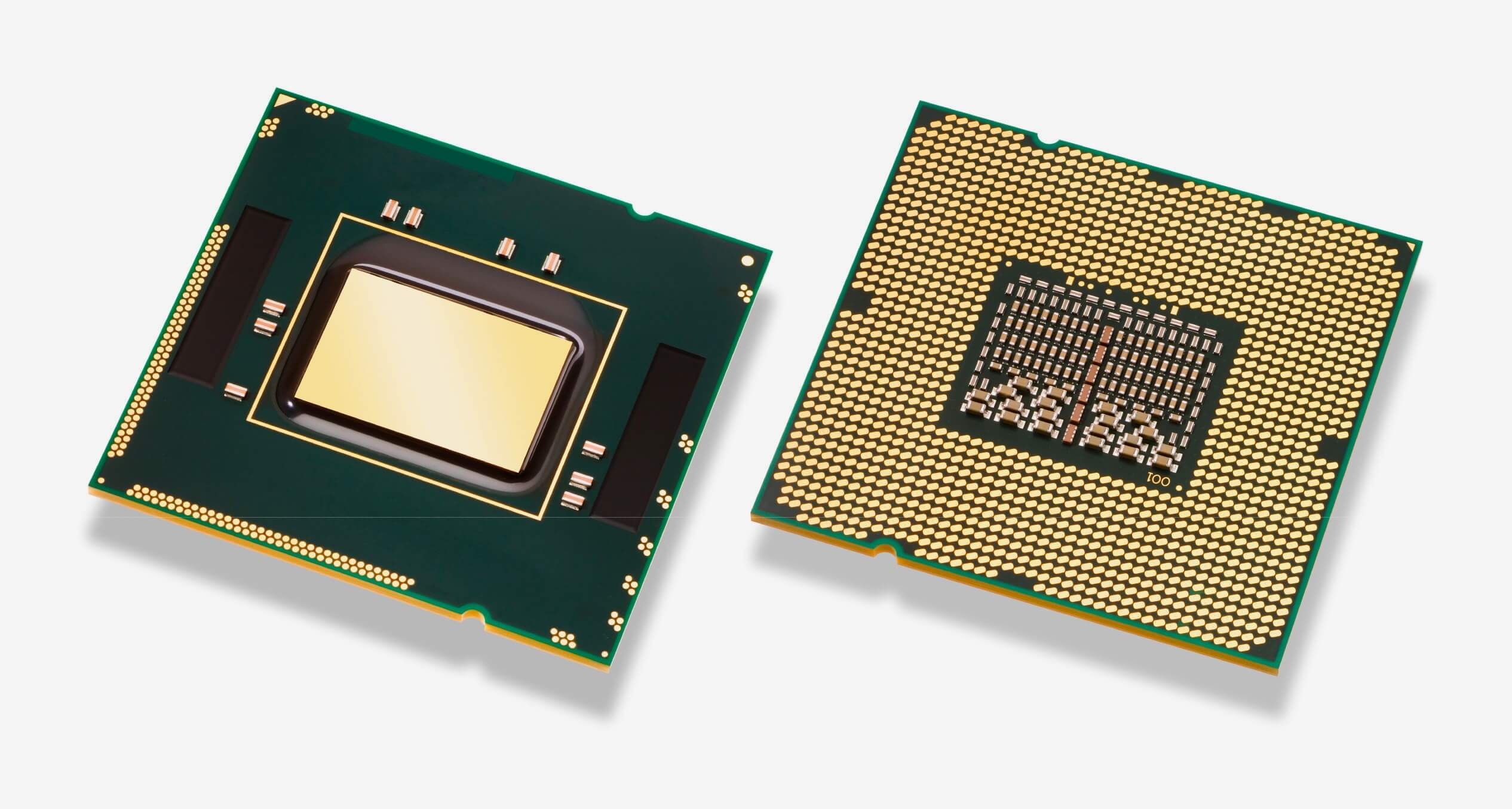

Современные процессоры имеют форму небольшого прямоугольника, который представлен в виде пластины из кремния. Сама пластина защищена специальным корпусом из пластмассы или керамики. Под защитой находятся все основные схемы, благодаря им и осуществляется полноценная работа ЦП. Если с внешним видом все предельно просто, то, что касается самой схемы и того, как устроен процессор? Давайте разберем это подробнее.

Как устроен процессор компьютера

В состав ЦП входит небольшое количество различных элементов. Каждый из них выполняет свое действие, происходит передача данных и управления. Обычные пользователи привыкли отличать процессоры по их тактовой частоте, количеству кэш-памяти и ядрам. Но это далеко не все, что обеспечивает надежную и быструю работу. Стоит уделить отдельное внимание каждому компоненту.

Архитектура

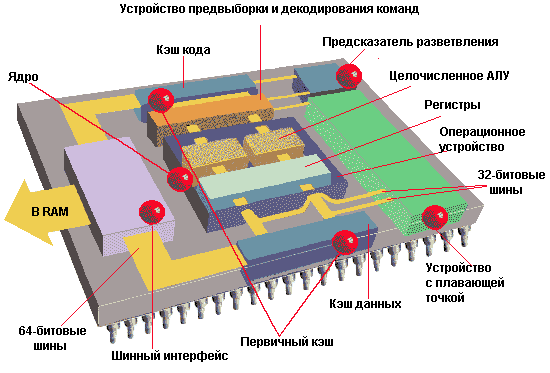

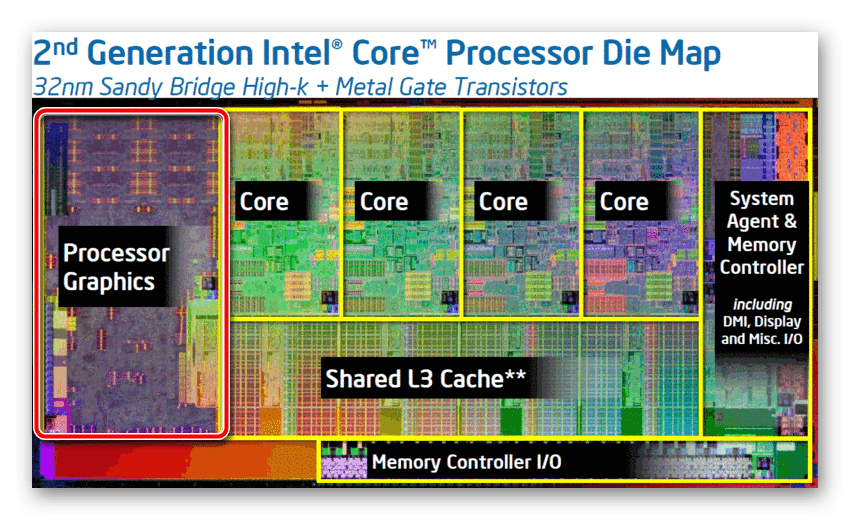

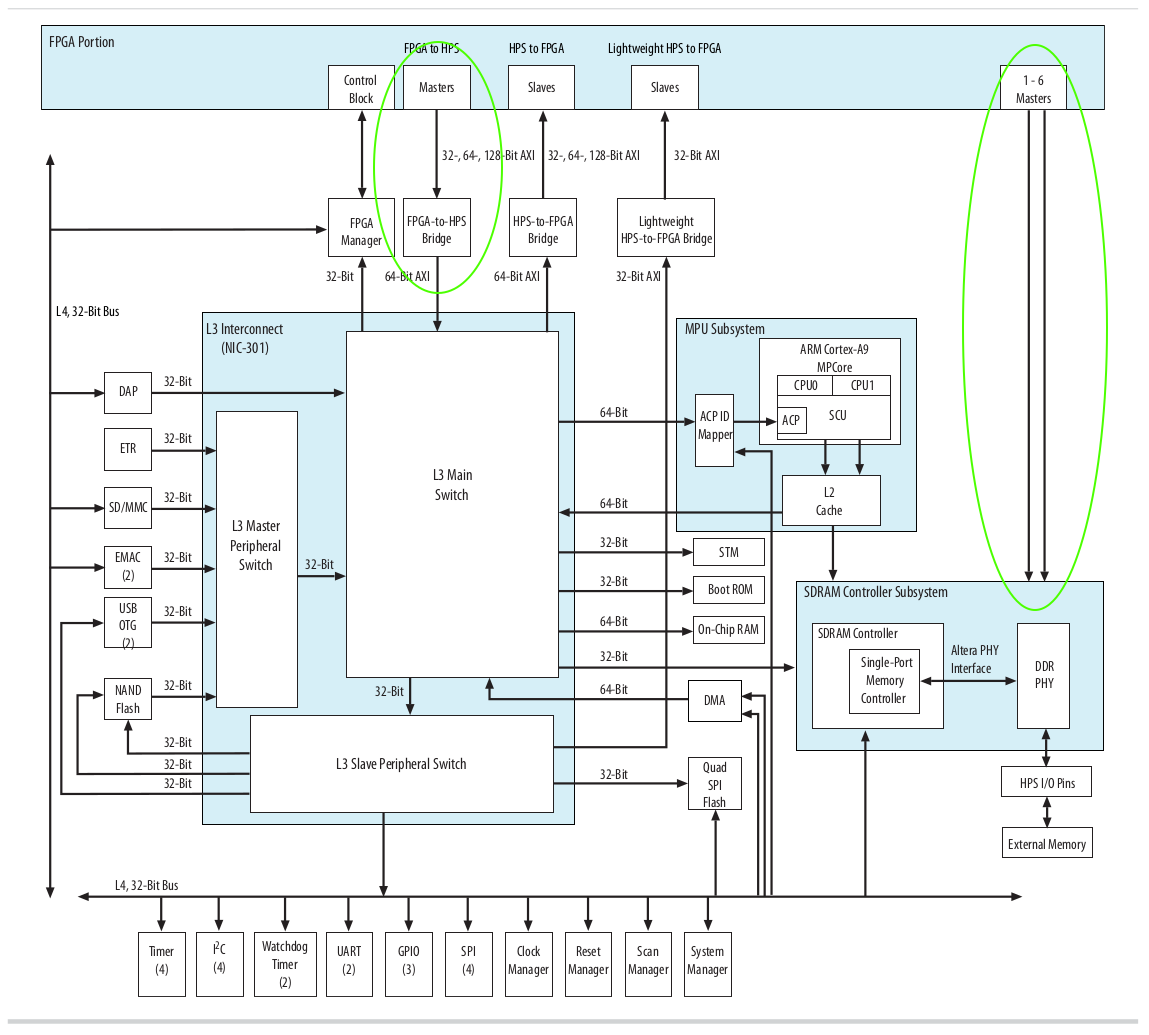

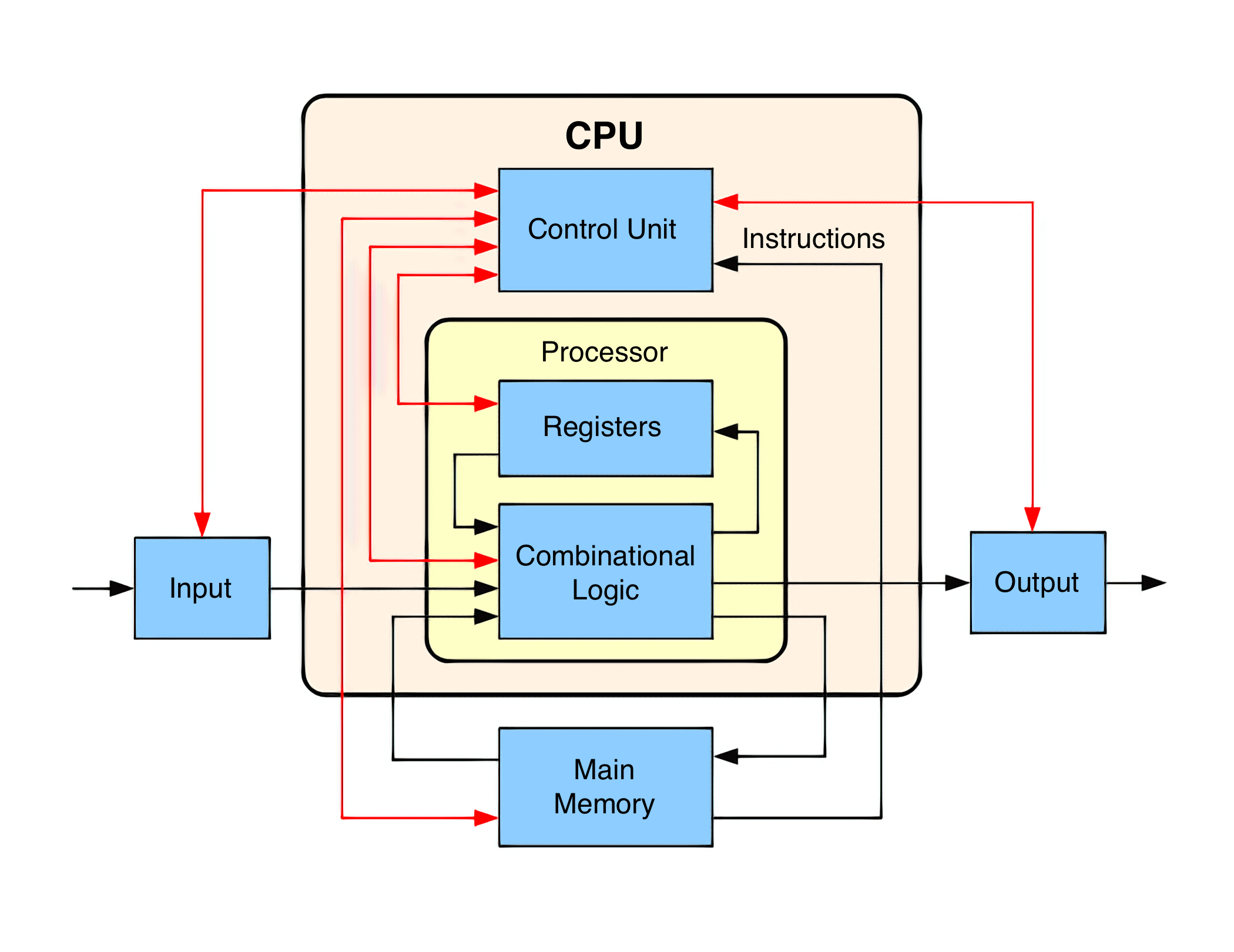

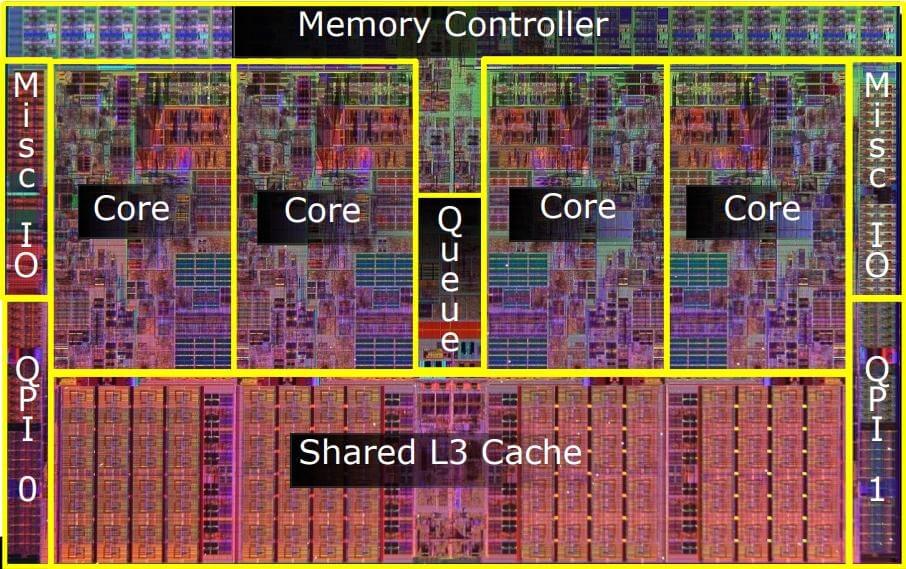

Внутренняя конструкция ЦП часто отличается друг от друга, каждому семейству присущ свой набор свойств и функций – это и называется его архитектурой. Пример конструкции процессора вы можете наблюдать на изображении ниже.

Но многие под архитектурой процессора привыкли подразумевать немного другое значение. Если рассматривать ее с точки зрения программирования, то она определяется по его возможности выполнять определенный набор кодов. Если вы покупаете современный CPU, то скорее всего он относится к архитектуре x86.

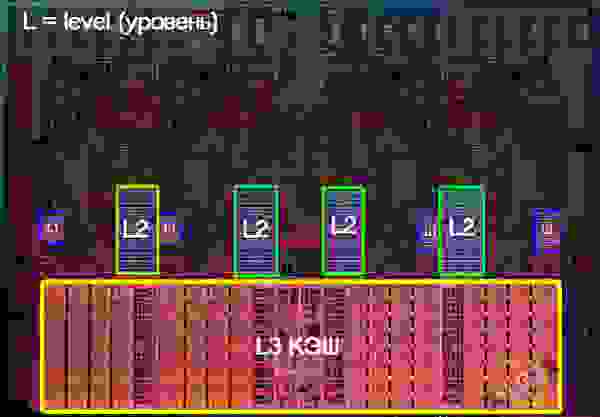

Основная часть CPU называется ядром, в нем содержатся все необходимые блоки, а также происходит выполнение логических и арифметических задач. Если вы посмотрите на рисунок ниже, то сможете разобрать как выглядит каждый функциональный блок ядра:

Системная шина

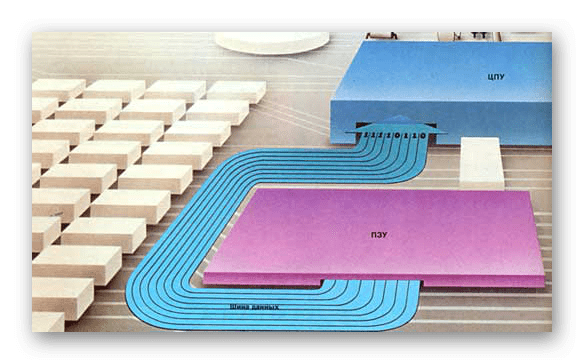

По системной шине CPU соединяются устройства входящие в состав ПК. К ней напрямую подключен только он, остальные элементы подсоединяются через разнообразные контроллеры. В самой шине присутствует множество сигнальных линий, через которые происходит передача информации. Каждая линия имеет свой собственный протокол, обеспечивающий связь по контроллерам с остальными подключенными компонентами компьютера. Шина имеет свою частоту, соответственно, чем она выше, тем быстрее совершается обмен информацией между связующими элементами системы.

Кэш-память

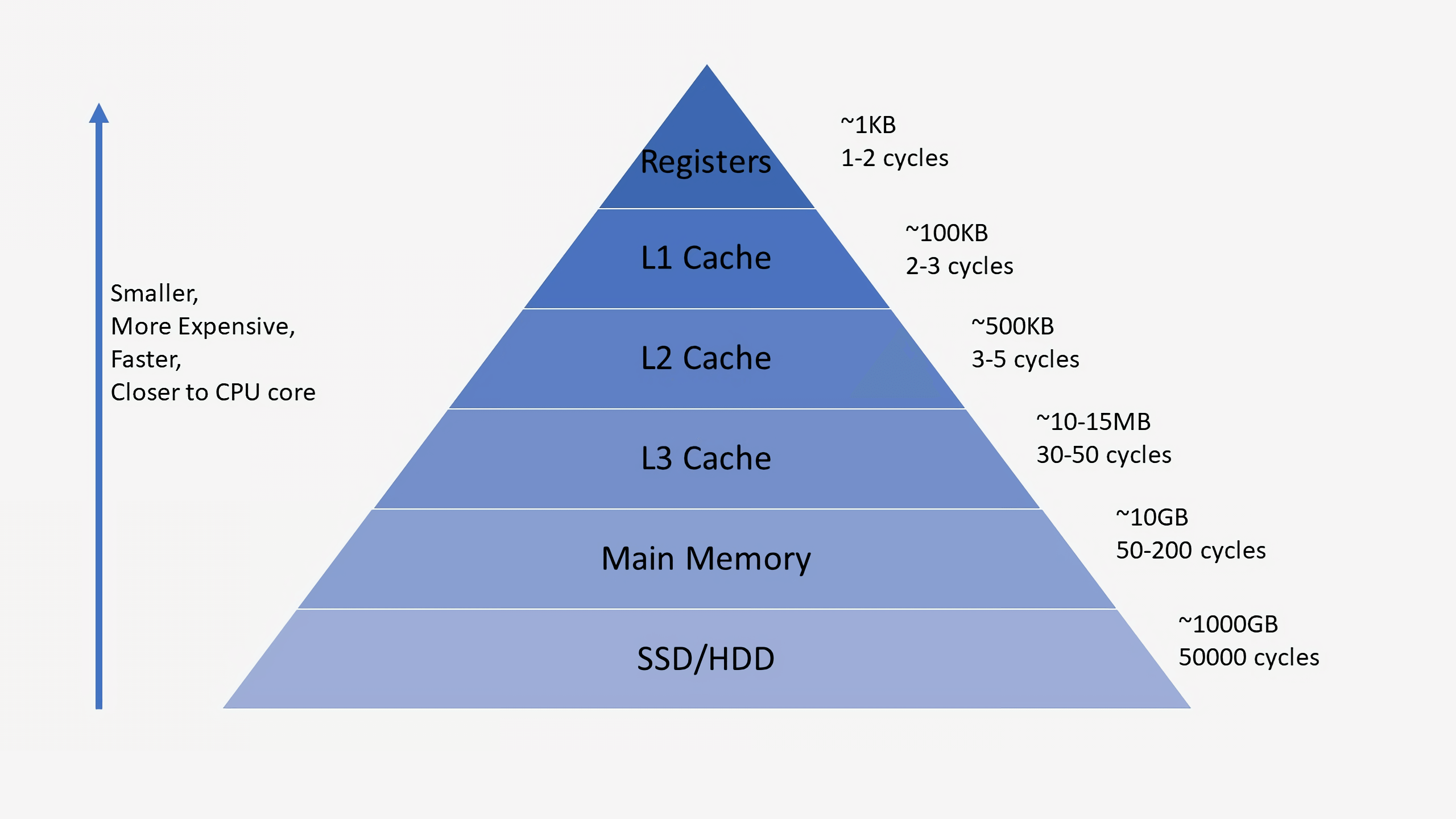

Быстродействие ЦП зависит от его возможности максимально быстро выбирать команды и данные из памяти. За счет кэш-памяти сокращается время выполнения операций благодаря тому, что она играет роль временного буфера, обеспечивающего мгновенную передачу данных CPU к ОЗУ или наоборот.

Основной характеристикой кэш-памяти является ее различие по уровням. Если он высокий, значит память более медленная и объемная. Самой скоростной и маленькой считается память первого уровня. Принцип функционирования данного элемента очень прост – CPU считывает из ОЗУ данные и заносит их в кэш любого уровня, удаляя при этом ту информацию, к которой обращались давно. Если процессору нужна будет эта информация еще раз, то он получит ее быстрее благодаря временному буферу.

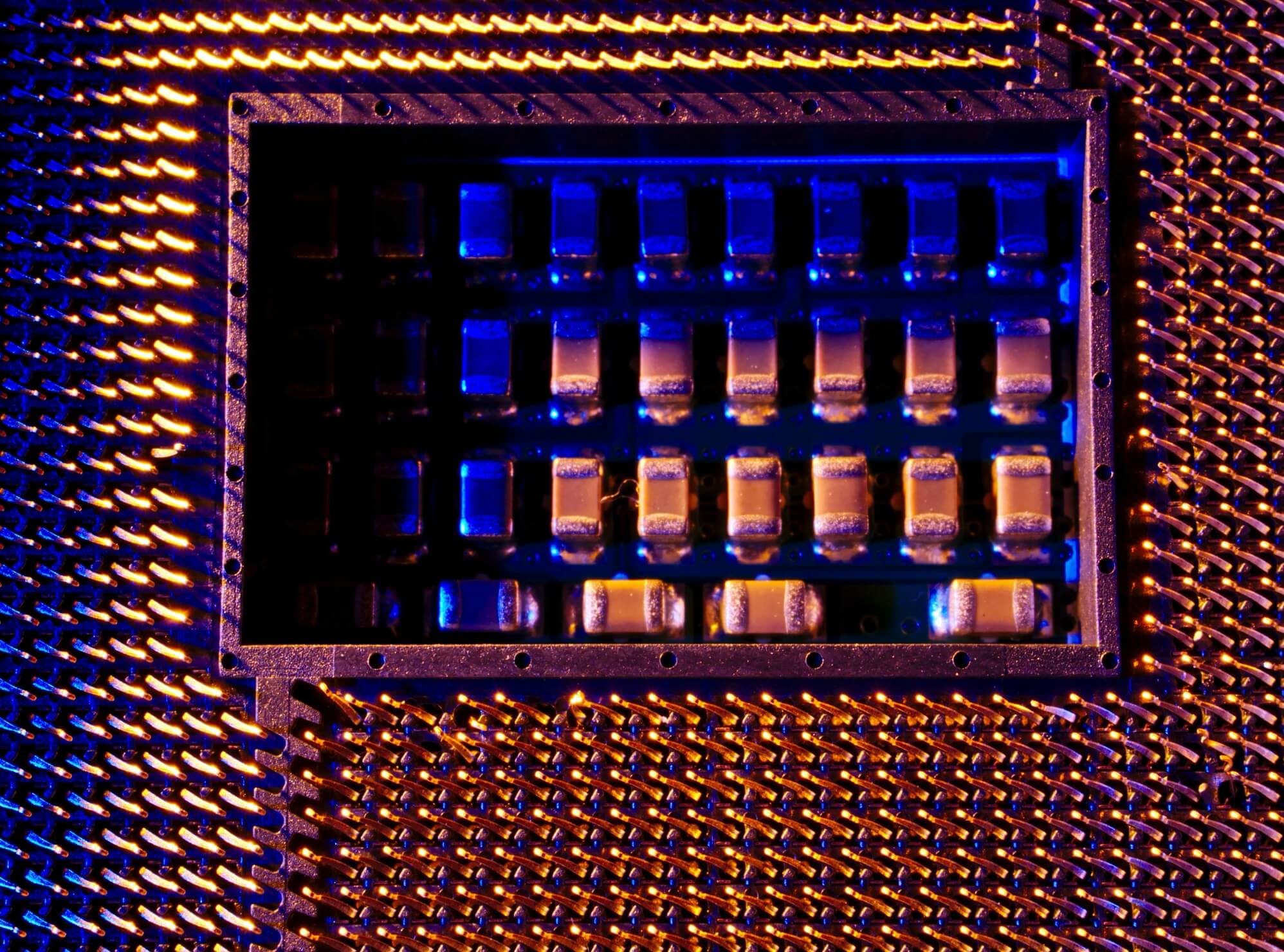

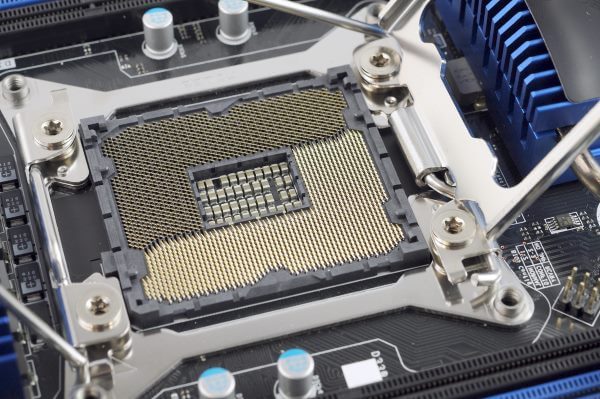

Сокет (разъем)

Благодаря тому, что процессор имеет собственный разъем (гнездовой или щелевой), вы можете легко заменить его при поломке или модернизировать компьютер. Без наличия сокета ЦП просто бы впаивался в материнскую плату, усложняя последующий ремонт или замену. Стоит обратить внимание – каждый разъем предназначен исключительно для установки определенных процессоров.

Часто пользователи по невнимательности покупают несовместимые процессор и материнскую плату, из-за чего появляются дополнительные проблемы.

Видеоядро

Благодаря внедрению в процессор видеоядра он выполняет роль видеокарты. Конечно, по мощности он с ней не сравнится, но если вы покупаете CPU для несложных задач, то вполне можно обойтись и без графической карточки. Лучше всего встроенное видеоядро показывает себя в недорогих ноутбуках и дешевых настольных компьютерах.

В этой статье мы подробно разобрали из чего состоит процессор, рассказали о роли каждого элемента, его важности и зависимости от других элементов. Надеемся, что эта информация была полезна, и вы узнали новое и интересное для себя из мира CPU.

Как на самом деле делают процессоры? РАЗБОР

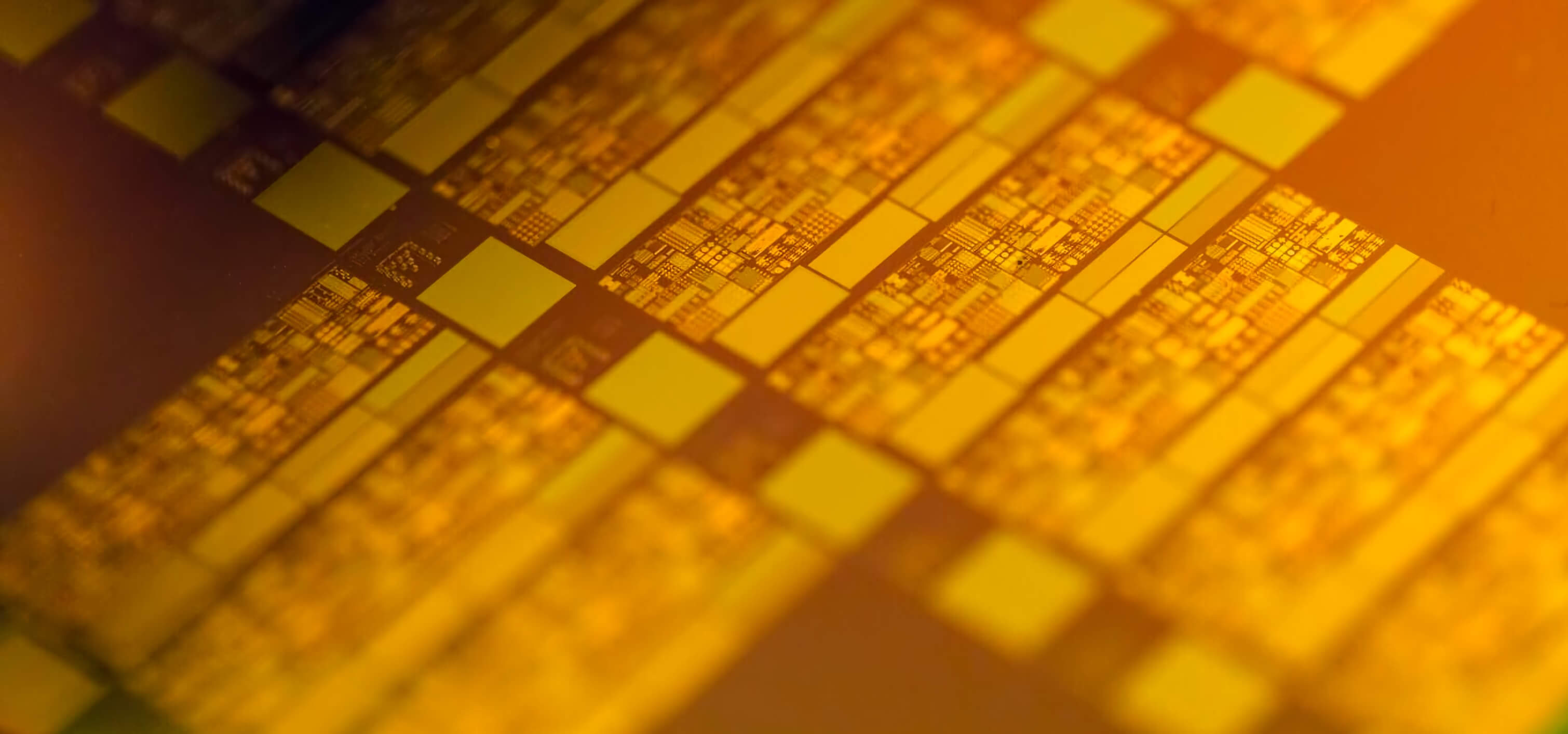

Как создаются современные процессоры? Насколько это сложный и интересный процесс и почему так важна некая Экстремальная УФ-литография? В этот раз мы копнули действительно глубоко и готовы рассказать вам об этой магии технологий. Располагайтесь поудобнее, будет интересно.

Вот вам затравочка — 30-килоВаттный лазер в вакууме стреляет по капле олова и превращает ее в плазму — скажете фантастика?

А мы разберемся как это работает и расскажем об одной компании из Европы, которая стоит тенью за всеми гигантами Apple, AMD, Intel, Qualcomm, Samsung и другими и без нее никаких новых процессоров бы и не было. И нет это, к сожалению, не Чебоксарский завод электроники.

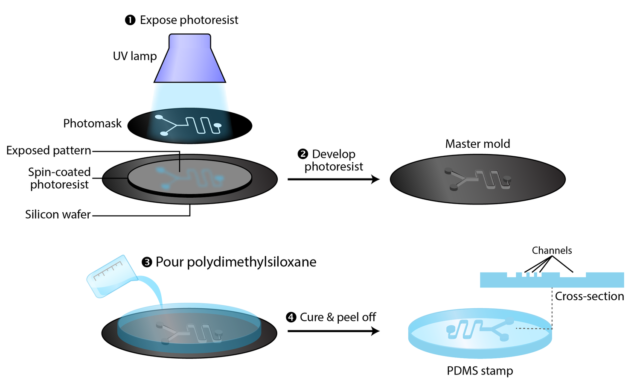

Фотолитография

Начнем с простого примера — возьмем прозрачное стекло и нанесем на него какой-то геометрический рисунок, оставив при этом какие-то участки без краски. По сути, сделаем трафарет. Приложим этот кусок стекла к фонарику и включим его. Мы получим ровно тот же рисунок в виде тени, который мы нанесли на кусок стекла.

В производстве процессоров этот кусок стекла с рисунком называется маска. Маска позволяет получить на поверхности любого материала “засвеченные и незасвеченные” участки любой плоской формы.

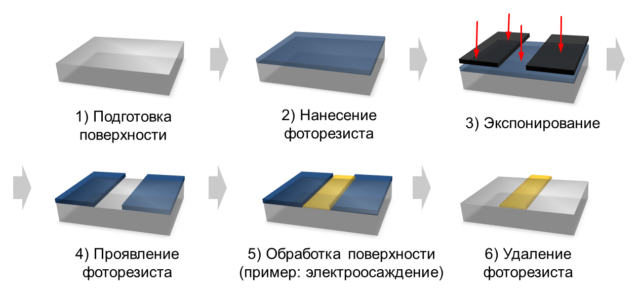

Хорошо — рисунок на поверхности мы получили, но это всего лишь тень. Теперь надо как-то его там сохранить. Для этого на поверхность кремниевой пластины наносится специальный светочувствительный слой, который называют Фоторезистом. Для простоты мы не будем тут говорить о позитивных и негативных фоторезистах, почему они так реагируют, все-таки мы не на уроке Физической химии. Просто скажем, что это такое вещество, которое меняет свои свойства, когда на него попадает свет на определенной частоте, то есть на определенной длине волны.

Опять же как и на фотопленке или фотобумаге — специальные слои материалов реагируют на свет!

После того как нужные нам участки на кремнии мы засветили, именно их мы можем убрать, оставив при этом на месте остальные, то есть незасвеченные участки. В итоге мы получили тот рисунок, который и хотели. Это и есть фотолитография!

Конечно, кроме фотолитографии в производстве процессоров участвуют и другие процессы, такие как травление и осаждение, фактически комбинацией этих процессов вместе с фотолитографией транзисторы как-бы печатаются слой за слоем на кремнии.

Технология не новая, почти все процессоры начиная с 1960-х производятся при помощи фотолитографии. Именно эта технология открыла мир полевых транзисторов и путь ко всей современной микроэлектронике.

Но по-настоящему большой скачок в этой области произошел только недавно! С переходом на EUV. И всё из-за длины волны в 13.5 нм. Не переживайте, сейчас объясню!

Длина волны на которой светит наш “фонарик” — это невероятно важный параметр. Именно она и определяет насколько маленьким вы можете получить элементы на кристалле.

Правило максимально простое: Меньше длина волны — больше разрешение, и меньше техпроцесс!

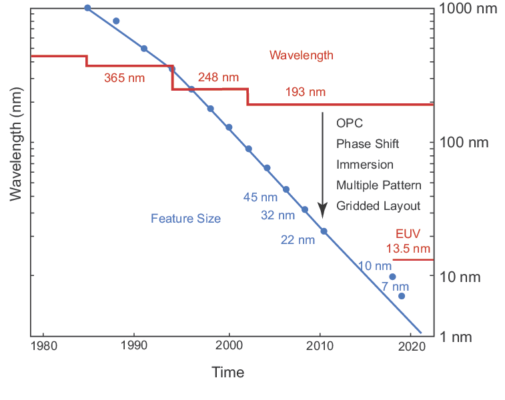

Обратите внимание на картинку. Абсолютно все процессоры начиная с начала 90-х до 2019 года производились с использованием процесса Глубокой УФ-литографии, или DUV литографии. Это то, что было до Экстремальной.

Он основывался на использовании фторид-аргонового лазера, который испускает свет с длиной волны в 193 нанометра. Этот свет лежит в области глубокого ультрафиолета — отсюда и название.

Он проходит через систему линз, маску и попадает на наш кристалл покрытый фоторезистом, создавая необходимый рисунок.

Но у этой технологии тоже были свои ограничения, завязанные на фундаментальных законах физики.

Какой же минимальный техпроцесс возможен? Смотрим на формулу (только не пугайтесь):

Здесь Лямбда — это и есть наша длина волны, а CD — это critical dimension, то есть минимальный размер получаемой структуры. То есть с использованием “старой” DUV литографии можно получить структуры не меньше примерно 50 нм. Но как же это так спросите вы? Ведь производители отлично делали и 14 и 10 нм, а кто-то даже и 7 нм с использованием DUV литографии.

Они пошли на хитрости. Вместо одного засвета через одну единую маску, они стали использовать несколько масок, с разными рисунками, которые дополняют друг-друга. Это процесс получил название множественное экспонирование. Назовем это принципом слоеного пирога!

Да — производители обошли прямые физические ограничения, но физику не обманули!

Появилась серьезная проблема: эти дополнительные шаги сделали производство каждого чипа гораздо дороже, из-за них увеличивается количества брака, есть и другие проблемы.

То есть в теории можно продолжить работать со старой технологией и путем игры с масками и экспонированием (двойная, тройная, четверная экспозиция) уменьшать размеры и дальше, но это сделает процы золотыми. Ведь с каждым слоем процент брака возрастает все выше, а ошибка накапливается!

То есть можно сказать, что DUV — это тупик! Что делать дальше, как уменьшать?

И тут на помощь приходит великая и ужасная технология Экстремальной УФ-литографии, или EUV-литографии!

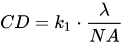

Посмотрите на фото — оно прекрасно демонстрирует различие двух технологий. Обе получены с использованием 7-нанометрового техпроцесса, но та что слева получена с использованием DUV-литографии и с теми самыми хитростями о которых мы говорили — тройное экспонирование, то есть с поэтапным использованием 3 разных масок. Справа же — технология EUV литографии на 13.5 нанометрах, с использованием одной единственной маски — разница очевидна — границы гораздо четче, лучший контроль геометрии, ну и сам процесс намного быстрее, меньше процент брака, то есть в конце концов дешевле. Вот она дорога в светлое будущее, почему бы сразу так не делать, в чем проблема?

Как работает EUV-литография

Все дело в том, что хоть EUV это та же литография, внутри в деталях все гораздо сложнее и тут ученые и инженеры столкнулись с новыми проблемами!

Сама технология экстремальной УФ-литографии начала разрабатываться в самом начале 2000 годов. В ней используется источник, который излучает свет с длинной волны в 13.5 нанометров — то есть на нижней границе УФ-спектра, близко к рентгену!

В теории этим способом можно создавать структуры уже критических размеров — настолько маленьких, что еще чуть-чуть и на них перестанут действовать законы обычной физики. То есть после 5 нм мы попадаем в квантовый мир!

Но даже эта проблема на данный момент решена. Есть источник — возьми, да и делай себе сколь угодно маленькие процессоры.

Все совсем не так просто!

Проблема таких коротких длин волн в том, что они поглощаются почти всеми материалами, поэтому обычные линзы что были раньше уже не подходят. Что делать?

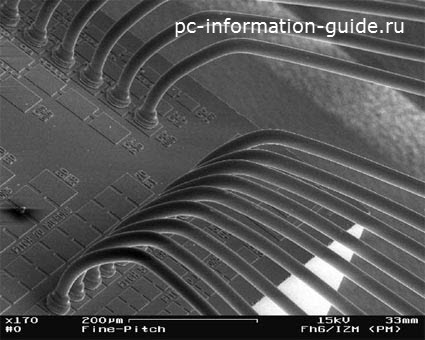

Для управления таким светом было принято решение создать специальные отражающие зеркальные линзы. И эти линзы должны быть гладкими! Очень гладкими. Практически идеально гладкими!

Вот вам аналогия — растянем линзу до размеров, скажем, Германии, так вот ее поверхность должна быть такой гладкой, что ничего не должно выпирать больше чем на 1 миллиметр. Этот параметр называется шероховатостью линзы и у нужной нам он должен быть меньше 0.5 нанометра. Это уже близко к размерам АТОМА! Кто же сможет подковать блоху?

Конечно, Zeiss — только они на это способны! Да — та самая компания Zeiss, чьи линзы стоят на моем фотике, были в Nokia или во флагманах Sony Xperia.

Одна проблема решена — линзы есть!

Есть и вторая — этот свет рассеивается даже в простом воздухе. Поэтому для того чтобы процесс прошел нормально его надо проводить в вакууме!

Про частички пыли и грязи я вообще молчу — понятно что их там вообще не должно быть. Чистые комнаты на таком производстве на порядки чище, чем операционные в больницах! Люди буквально ходят в скафандрах. Любая, даже самая маленькая частичка грязи, кожи или воздуха может испортить и маску и зеркала!

А что же с источником? Просто поставили специальный лазер на более короткую длину волны и все? Проблема в том, что ни лампочек, ни лазеров, ни каких-либо других нормальных источников света, которые излучают на такой длине волны просто не существует в природе.

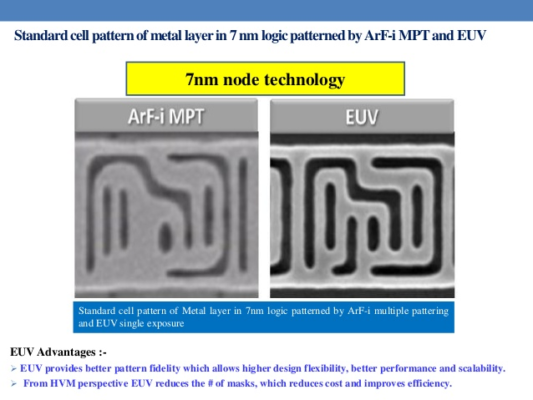

И как же тогда получают нужное излучение? Элементарно, Ватсон — нам нужна плазма.

Надо нагреть оловянный пар до температур в 100 раз больших, чем температура поверхности солнца! Всего-то! И за этим стоит почти 2 десятилетия разработок.

В установке для производства процессоров по EUV-литографии, о которой мы поговорим отдельно установлен специальный углекислотный лазер, который опять же может производиться в тандеме всего двух компаний в мире — немецкой фирмой Trumpf и американской Cymer. Этот монстр мощностью в 30 киловатт стреляет по 2 импульса с частотой 50 килогерц.

Лазер попадает в капли олова, первый выстрел фактически плющит и превращает каплю в блин, которая становится легкой мишенью для второго залпа, который ее поджигает. И происходит это 50 тысяч раз в секунду! А образовавшаяся плазма и излучает этот свет в экстремальном УФ спектре.

И естественно, это только самая база, но мы попробовали нарисовать вам картину того насколько это сложный и крутой процесс.

Компания, стоящая за производством всех процессоров

О технологии рассказали, значит ее кто-то придумал и реализовал, но ее разработка оказалась настолько дорогой, что даже крупные гиганты и воротилы не способны потянуть такие бюджеты!

В итоге, чтобы это стало реальностью всем пришлось скинуться — Intel в 2012 году, а TSMC и Samsung где-то в 2015 году приняли участие в общем проекте. Суммарные инвестиции составили, по разным оценкам от 14 до 21 млрд долларов! Из которых почти 10 млрд были вложены в одну единственную нидерландскую компанию ASML. Именно она и стоит за всем производством процессоров в мире по методу EUV-литографии! Вау! Что за ASML и почему мы о ней ничего не слышали? Компания из Нидерландов — что за темная лошадка?

Все дело в том, что ASML создали тот самый инструмент без которого Apple, Самсунг и Intel с AMD фактически как без рук! Речь идет об установке стоимостью более 120 миллионов долларов. Она огромная, 180-тонная, потребляет почти 1 мегаватт электроэнергии, и ей нужно почти 1.5 тонны воды в минуту для охлаждения! Но даже при такой цене очереди на них стоят годами ведь в год этих машин производится несколько десятков штук.

Тут же стоит упомянуть немалый вклад российских умов. Например, один из создателей этой технологии — Банин Вадим Евгеньевич, сейчас директор по разработке в ASML. Также в компании работают и другие наши соотечественники!

Мы выяснили, что эта компания делает одни из самых технологичных девайсов, в котором собраны все знания человечества и на них производят процессоры все IT-гиганты сразу!

Но не только ASML стоит за спиной нам известных IT-гигантов. Их установки состоят из более чем 100 тысяч деталей, которые производятся более чем тысячью компаний по всему миру. Все эти компании связаны друг с другом!

Будущее

Но что же будет дальше! Вы что — думали, что мы оставим вас оставим в дне сегодняшнем? Нет — мы подглядели в будущее! Мы раздобыли информацию что будет после пяти или даже двух нм!

Во-первых, прямо сейчас, пока вы смотрите это видео, TSMC уже штампует новые процессоры для HUAWEI, Apple и Samsung с использованием EUV-литографии, но не на 7 нм, как было с Apple A13 и Kirin 990, а на 5 нм техпроцессе! И этому есть множества подтверждений! И о них мы услышим уже этой осенью. Как вам такое — A14 Bionic будет 5нм! Так же ждем новые Exynos на 5 нм и процессоры Google, о которых мы рассказывали отдельно! Qualcomm наверняка тоже подтянется за ними, но тут мы не располагаем данными!

А во-вторых, и это вообще взрывает мозг, ASML уже заканчивает разработку установок, которые позволят производить процессоры на 2 нанометровом техпроцессе и даже меньше всего через 4-5 лет!

Для этого ребята из нидерландской компании совместно с немецкой Zeiss разработали новые зеркальные линзы, с высокими значениями апертуры. Это анаморфная оптика — она и многое другое позволит увеличить разрешающую способность.

Сам процесс по сути тот же EUV, но с приставкой High-NA EUV. А сами агрегаты будут занимать еще больше места, посмотрите вот так для них делают оптику!

Этот год тяжелый для всех, но в тоже время — посмотрите какими шагами начинают развиваться технологии, все шире и шире. Нас ждут новые процессоры с мощностями, которые нам и не снились.

Кроме этого развиваются совершенно новые типы процессоров такие как NPU — для нейровычислений.

Собственная платформа. Часть 0.1 Теория. Немного о процессорах

Здравствуй, мир! Сегодня у нас серия статьей для людей со средними знаниями о работе процессора в которой мы будем разбираться с процессорными архитектурами (у меня спелл чекер ругается на слово Архитектурами/Архитектур, надеюсь я пишу слово правильно), создавать собственную архитектуру процессора и многое другое.

Принимаются любые замечания!

Немного про архитектуру процессора

Исторически сложилось, что существуют много процессоров и много архитектур. Но многие архитектуры имеют схожести. Специально для этого появились «Группы» архитектур типа RISC, CISC, MISC, OISC (URISC). Кроме того они могут иметь разные архитектуры адресации памяти (фон Неймана, Гарвард). У каждого процессора есть своя архитектура. Например большинство современных архитектур это RISC (ARM, MIPS, OpenRISC, RISC-V, AVR, PIC** и т.д.), но есть архитектуры которые выиграли просто за счет других факторов (Например удобство/цена/популярность/etc) Среди которых x86, x86-64 (Стоит отметить, что x86-64 и x86 в последних процессорах используют микрокод и внутри них стоит RISC ядро), M68K. В чем же их отличие?

Reduced Instruction Set Computer — Архитектура с уменьшенным временем выполнения инструкций (из расшифровка RISC можно подумать, что это уменьшенное количество инструкций, но это не так). Данное направления развилось в итоге после того, как оказалось, что большинство компиляторов того времени не использовали все инструкции и разработчики процессоров решили получить больше производительности использую Конвейеры. В целом RISC является золотой серединой между всеми архитектурами.

Яркие примеры данной архитектуры: ARM, MIPS, OpenRISC, RISC-V

Что такое TTA? ТТА это Архитектура на основе всего одной инструкции перемещения из одного адреса памяти в другую. Данный вариант усложняет работу компилятора зато дает большую производительность. У данной архитектуры есть единственный недостаток: Сильная зависимость от шины данных. Именно это и стало причиной ее меньшей популярности. Надо отметить что TTA является разновидностью OISC.

Яркие примеры: MOVE Project

OISC (URISC)?

One Instruction Set Computer — Архитектура с единственной инструкцией. Например SUBLEQ. Такие архитектуры часто имеют вид: Сделать действие и в зависимости от результата сделать прыжок или продолжить исполнение. Зачастую ее реализация достаточно простая, производительность маленькая, при этом снова ограничение шиной данных.

Яркие примеры: BitBitJump, ByteByteJump, SUBLEQ тысячи их!

CISC — Complex Instruction Set Computer — ее особенность в увеличенных количествах действий за инструкцию. Таким образом можно было теоретически увеличить производительность программ за счет увеличения сложности компилятора. Но по факту у CISC плохо были реализованы некоторые инструкции т.к. они редко использовались, и повышение производительности не было достигнуто. Особенностью этой группы является еще ОГРОМНАЯ Разница между архитектурами. И несмотря на названия были архитектуры с маленьким количеством инструкций.

Яркие примеры: x86, M68K

Адресация памяти

Архитектура фон Неймана

Особенностью таких архитектур была общая шина данных и инструкций. Большинство современных архитектур это программный фон Нейман, однако никто не запрещает делать аппаратный Гарвард. У данной архитектуры большим недостатком является большое зависимости производительности процессора от шины. (Что ограничивает общую производительность процессора).

Архитектура гарварда

Особенность этой архитектуры является отдельная шина данных и инструкций. Дает большую производительность чем фон Нейман за счет возможности за один такт использовать обе шины (читать из шины инструкций и одновременно записывать в шинну данных), но осложняет архитектуру и имеет некоторые ограничения. В основном используется в микроконтроллерах.

Особенности процессоров

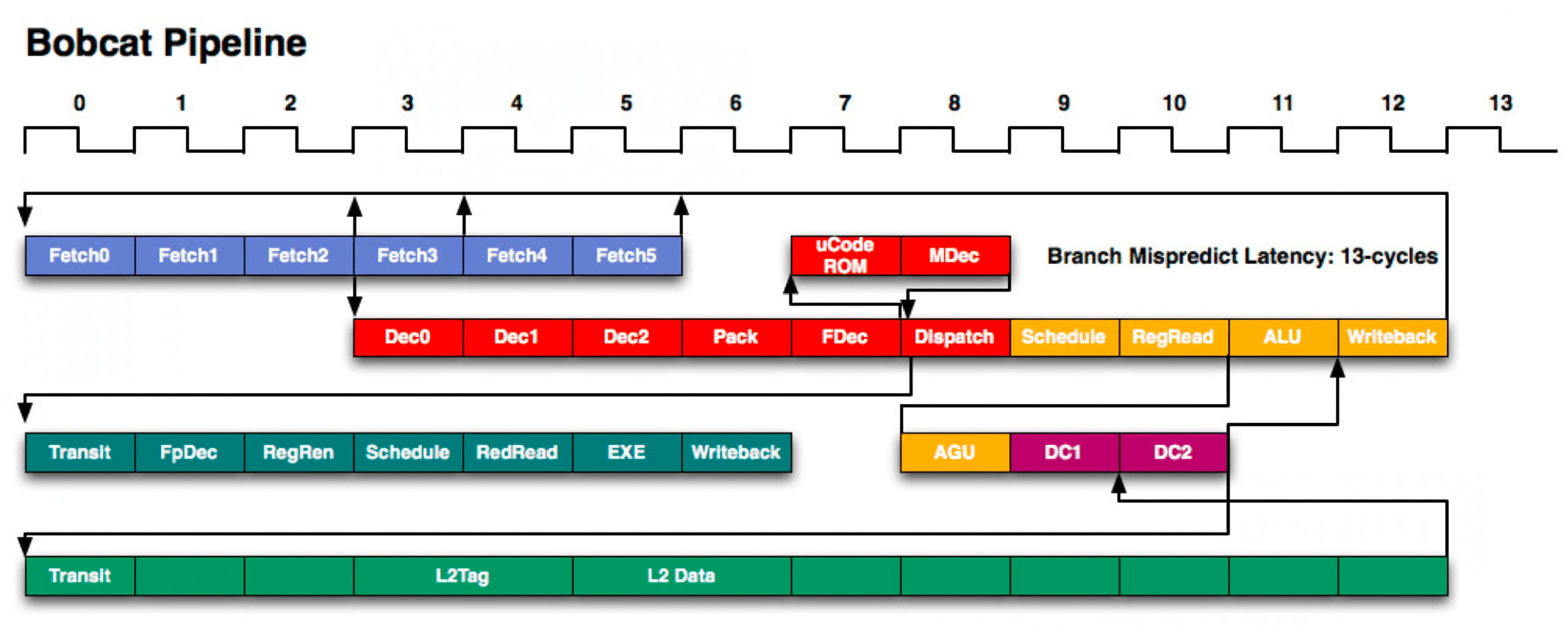

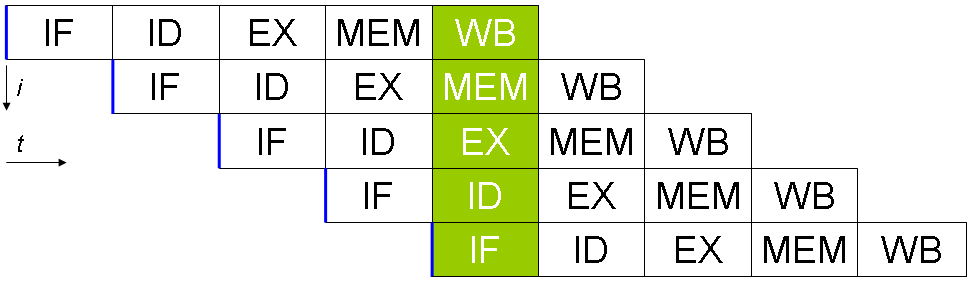

Конвейеры

Что такое конвейеры? Если сказать очень глупым языком это несколько параллельных действий за один такт. Это очень грубо, но при этом отображает суть. Конвейеры за счет усложнения архитектуры позволяют поднять производительность. Например конвейер позволяет прочитать инструкцию, исполнить предыдущую и записать в шину данных одновременно.

На картинке более понятно, не правда?

IF — получение инструкции,

ID — расшифровка инструкции,

EX — выполнение,

MEM — доступ к памяти,

WB — запись в регистр.

Вроде все просто? А вот и нет! Проблема в том что например прыжок (jmp/branch/etc) заставляют конвейер начать исполнение (получение след. инструкции) заново таким образом вызывая задержку в 2-4 такта перед исполнение следующей инструкции.

Расширение существующих архитектур

Достаточно популярной техникой является добавление в уже существующую архитектуру больше инструкций через расширения. Ярким примером является SSE под x86. Этим же грешит ARM и MIPS и практически все. Почему? Потому что нельзя создать унивирсальную архитектуру.

Другим вариантом является использование других архитектур для уменьшения размера инструкций.

Яркий пример: ARM со своим Thumb, MIPS с MIPS16.

Техники применяемые в GPU

В видеокартах часто встречается много ядер и из-за этой особенности появилась потребность в дополнительных решениях. Если конвейеры можно встретить даже в микроконтроллерах то решения используемых в GPU встречаются редко. Например Masked Execution (Встречается в инструкциях ARM, но не в Thumb-I/II). Еще есть другие особенность: это уклон в сторону Floating Number (Числа с плавающей запятой), Уменьшение производительности в противовес большего количества ядер и т.д.

Masked Execution

Данный режим отличается от классических тем, что инструкции исполняются последовательно без использования прыжков. В инструкции хранится некоторое количество информации о том при каких условия эта инструкция будет исполнена и если условие не соблюдено то инструкция пропускается.

Ответ прост! Что бы не нагружать шину инструкций. Например в видеокартах можно загрузить тысячи ядер одной инструкцией. А если бы использовалась система прыжков то пришлось бы для каждого ядра ждать инструкцию из медленной памяти. Кеш частично решает проблему, но все еще не решает проблему полностью.

Прочее

Здесь мы будем описывать несколько техник используемых в центральный процессорах и микроконтроллерах.

Прерывания

Прерывания это техника при которой исполняемый в данный момент код приостанавливается для выполнения какой-то другой задачи при каких-то условиях. Например при доступе в несуществующий участок памяти вызывается HardFault или MemoryFault прерывания или исключения. Или например если таймер отсчитал до нуля. Это позволяет не бездействовать пока нужно ждать какое-то событие.

Какие недостатки? Вызов прерывания это несколько тактов простоя и несколько при возврате из прерывания. Так же несколько инструкций в начале кода будет занято инструкциями для Таблицы прерываний.

Exception (исключения)

Но кроме прерываний еще существуют исключений которые возникают например при деления на ноль. Зачастую его совмещают с прерываниями и системными вызовами, как например в MIPS. Исключения не всегда присутствуют в процессоре например как в AVR или младших PIC

Системные вызовы

Системные вызовы используется в Операционных системах для того, чтобы программы могли общаться с операционной системой например просить ОС прочитать файл. Очень похоже на прерывания. Аналогично исключениям не всегда присутствуют в процессоре

Контроллеры доступа в память и прочие методы сдерживания программ

Здесь описываются методы запрета доступа приложений к аппаратуре напрямую.

Привилегированный режим

Это режим в котором стартует процессор. В таком режиме программа или ОС имеют полный доступ к памяти в обход MMU/MPU. Все программы запускаются в непривилегированном режиме во избежания прямого доступа к аппаратным подсистемам программ для этого не предназначенных. Например вредоносным программам. В Windows ее часто называют Ring-0, а в *nix — системным. Не стоит путать Привелигированный пользователь и Привилегированный режим ибо в руте вы все еще не можете иметь прямой доступ к аппаратуре (можно загрузить системный модуль который позволит это сделать, но об этом чуть позже 🙂

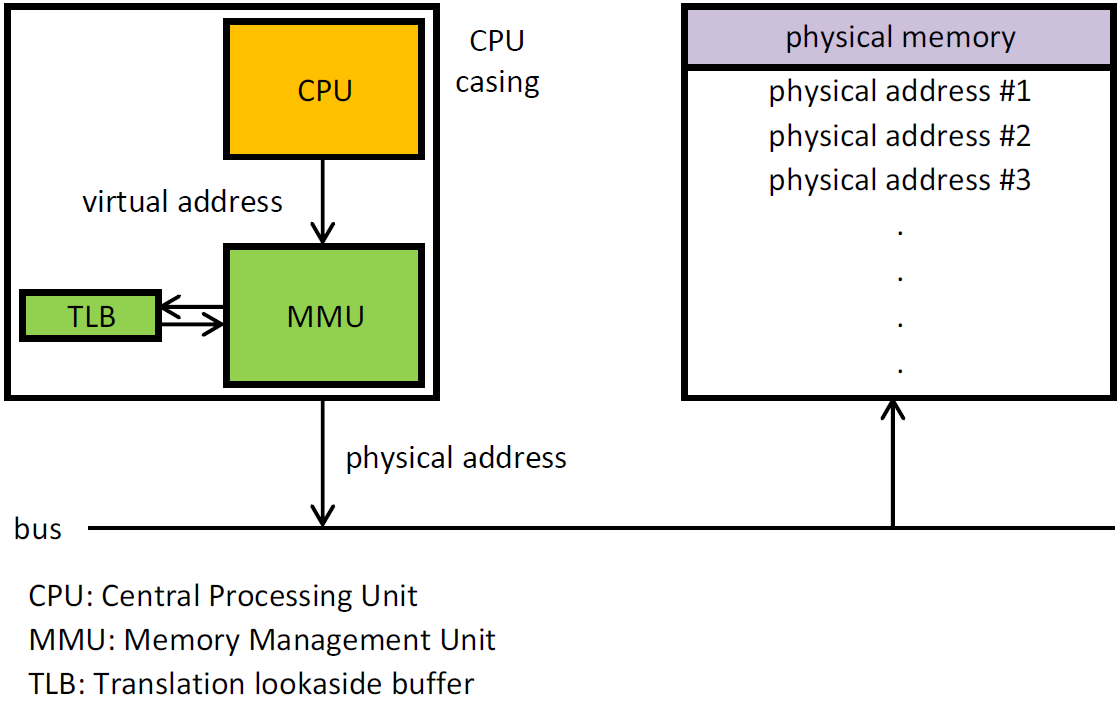

MPU и MMU

MPU и MMU используется в современных системах чтобы изолировать несколько приложений. НО если MMU позволяет «передвинуть» память то MPU позволяет только блокировать доступ к памяти/запуск кода в памяти.

PIC (PIE)

Что такое PIE? (PIC не использую для избежания путаницы с МК PIC). PIE это техника благодаря которой компилятор генерирует код который будет работать в любом месте в памяти. Эта техника в совмещении с MPU позволяет компилировать высокие языки программирования которые будут работать и с MPU.

Популярная техника SIMD используется для того, что бы за один такт выполнять несколько действий над несколькими регистрами. Иногда бывают в качестве дополнений к основной архитектуре, например, как в MIPS, ARM со своими NEON/VFP/etc, x86 со своим SSE2.

Reposition for Optimization

Это техника Используется для оптимизации кода, генерируемого компилятором, с помощью пересортировки инструкций, увеличивая производительность процессора. Это позволяет использовать конвейер на полную.

Status register

Что такое регистр статуса? Это регистр который хранит состояние процессора. Например находится ли процессор в привилегированном режиме, чем закончилась операция последнего сравнения.

Используется в связке с Masked Execution. Некоторые разработчики специально исключают регистр статуса ибо он может являться узким местом как поступили в MIPS.

В MIPS нет отдельной инструкции загрузки константы в память, но есть инструкция addi и ori которая позволяет в связке с нулевым регистром ($0) эмулировать работу загрузки константы в регистр. В других архитектурах она присутствует. Я затронул эту тему, потому что она пригодиться нам в статьях с практикой.

Rd, Rs vs Rd, rs, rt

Идут множество споров насчет того сколько должно быть операндов в арифметических инструкциях. Например в MIPS используется вариант с 3-мя регистрами. 2 операнда, 1 регистр записи. С другой стороны, использование двух операндов позволяет сократить код за счет уменьшения размера инструкции. Пример совмещения является MIPS16 в MIPS и Thumb-I в ARM. В плане производительности они практически идентичны (Если исключать размер инструкции как фактор).

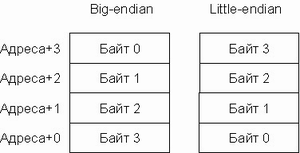

Endianness

Порядок байт. Возможно вам знакомы Выражения Big-Endian и Little-Endian. Они описывают порядок байт в инструкциях/в регистрах/в памяти/etc. Здесь думаю все просто :). Есть процессоры которые совмещают режимы, как MIPS, или которые используют одну систему команд, но имеют разный порядок байт, например ARM.

Битность процессора

Итак, что такое битность процессора? Многие считают, что это битность шины данных, но это не так. Почему? В ранние переоды микроконтроллеров и микропроцессоров шина могла быть, например, 4-х битной, но передавала пакетами по 8 бит. Для программы казалось, что это 8-и битный режим, но это была иллюзия, как и сейчас. Например, в ARM SoC-ах часто применяют 128-и битную шину данных или инструкций.

Сопроцессоры

Что такое сопроцессоры? Сопроцессоры являются элементами процессора или внешней микросхемой. Они позволяют исполнять инструкции, которые слишком громоздки для основной части процессора. Как яркий пример, сопроцессоры в MIPS для деления и умножения. Или например 387 для 80386, который добавлял поддержку чисел с плавающей запятой. А в MIPS сопроцессоров было много и они выполняли свои роли: контролировали прерывания, исключения и системные вызовы. Часто сопроцессоры имеют собственные инструкции и на системах, где этих инструкций нет, (пример ARM) эмулируют ее через Trap-ы (ловушки?). Несмотря на костыльность и маленькую производительность, они часто являются единственным выбором в микроконтроллерах.

Атомарность операций

Атомартность операций обеспечивает потоко-независимое исполнение за счет инструкций, которые выполняют несколько действий за один псевдотакт.

Вариант другого решения атомарность переферии. Например для установки ножки в STM32 в высокое и низкое состояние используется разные регистры, что позволяет иметь атомарность на уровне переферии.

Вы, навярняка, слышали о L1, L2, L3 и регистрах. Если коротко, процессор анализирует часть кода, чтобы предугадать прыжки и доступ в память и зараннее просит кеш получить эти данные из памяти. Кеш зачастую бывает прозрачным для программы, но бывают и исключения из этого правила. Например, в программных ядрах в ПЛИС используется програмный кеш.

И вы кончено слышали о такой вещи, как Cache Miss или промах по кешу. Это операция которая не была предусмотрена процессорам или процессор не успел закешировать эту часть памяти. Что достаточно часто является проблемой замедления доступа к памяти. Промах проходит незаметно для программы, но не останутся незаметными просадки в производительности.Так же переключения контекстов например при прерываниях тоже заставляет страдать кеш ибо небольшой код сбивает конвейер и кеш для собственных нужд.

Shadow Registers

В современных процессорах часто используется техника теневых регистров. Они позволяют переключаться между прерываниями и пользовательским кодом практически без задержек связанных с сохранением регистров.

Stack

Спросите тогда что такое куча (Heap)? Куча это память размером намного больше чем стек (Стек обычно

1MB). В хипе храниться все глобальное. Например все указатели полученные с помощю Malloc указывают на часть куча. А указатели хранятся в стеке или в регистрах. С помощью инструкций загрузки данных относительно регистра можно ускорить работу стека и других доступов к памяти по типу стека, поскольку не нужно постоянно использовать операции PUSH/POP, INC/DEC или ADDI, SUBI (добавить константу), чтобы получить данные глубже по стеку, а можно просто использовать доступ относительно стека с отрицательным смещением.

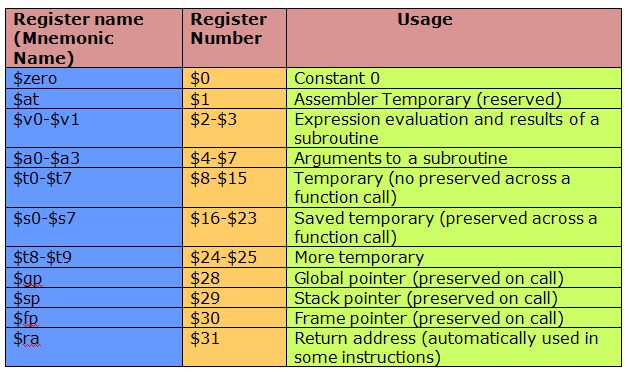

Регистры

Не буду описывать регистры слишком подробно. Это мы затронем в практической статье.

В x86 регистров достаточно мало. В MIPS используется увеличенное количество регистров, а именно 31 ($0 имеет значение всегда равное нулю). В процессоре университета Беркли использовались регистровые окна, которые жестки ограничивали вложенность функций, при этом имея лучшую производительность. В других же, таких как AVR, ограничили использование регистров. Для примера: три 16-битных можно трактовать как шесть восьмибитных, где первые 16ть недоступны при некоторых операциях. Я считаю, что лучший метод был выбран MIPS-ом. Это мое сугубо личное мнение.

Выравнивание

Что такое выравнивание? Оставлю-ка я этот вопрос вам 🙂

Конец

Это конец первой главы нулевой части. Вся серия будет крутиться вокруг темы создания собственного процессора. Собственной операционной системы. Собственного ассемблера. Собственного компилятора и много чего другого.

Из чего состоит центральный процессор?

Центральный процессор часто называют «мозгом» компьютера, ведь он, как и человеческий мозг, состоит из нескольких частей, собранных воедино для работы над информацией. Среди них есть те, что отвечают за прием информации, ее хранение, обработку и вывод. В этой статье портал TechSpot разбирает все ключевые элементы процессора, за счет которых и работают ваши компьютеры.

Этот текст входит в серию статей, в которых тщательно разбирается работа ключевых компонентов компьютера. Кроме того, если вы заинтересовались темой, рекомендуем ознакомиться с переводами статей серии «Как разрабатываются и создаются процессоры?».

Итак, приступим. Любому вычислительному устройству нужно нечто наподобие центрального процессора. По сути, программист пишет код для выполнения собственных целей, а затем процессор выполняет его для получения необходимого результата. Процессор также подключен к другим частям системы, вроде памяти и устройств ввода/вывода, чтобы обеспечить загрузку необходимых данных, но в этой статье мы не будем акцентировать на них внимание.

Фундамент любого процессора: архитектура набора команд

Чуть менее распространенными и более нишевыми являются MIPS, RISC-V и PowerPC. Архитектура набора отвечает за ряд основных вещей: какие инструкции процессор может обрабатывать, как он взаимодействует с памятью и кэшем, как задача распределяется по нескольким этапам обработки и др.

Чтобы лучше понять устройство процессора, разберем его элементы в том порядке, по которому выполняются команды. Различные типы инструкций могут следовать разными путями и использовать разные компоненты ЦП, поэтому здесь они будут обобщены, чтобы охватить максимум. Начнем с базового дизайна одноядерных процессоров и постепенно будем переходить к более продвинутым и сложным экземплярам.

Блок управления и исполнительный тракт

Исполнительный тракт подобен двигателю и, как следует из названия, это путь, по которому данные передаются при их обработке. Он получает входные данные, обрабатывает их и отправляет в нужное место после завершения операции. Блок управления, в свою очередь, направляет этот поток данных. В зависимости от инструкции, исполнительный тракт будет направлять сигналы к различным компонентам процессора, включать и выключать различные части пути, а также отслеживать состояние всего процессора.

3 основных типа команд

Команда памяти может представлять собой нечто вроде «прочтите значение из адреса памяти 1234 вместо значения А» или «запишите значение Б в адрес памяти 5678». Арифметические команды имеют вид в духе «добавьте значение А к значению Б и сохраните результат в значении В». Инструкции перехода, в свою очередь, похожи на «выполните этот код, если значение В положительное, или выполните другой код, если значение В отрицательное». Зачастую в программах используется цепочка сразу из нескольких вышеупомянутых примеров, из-за чего конечный результат выглядит примерно так: «добавьте значение адреса памяти 1234 к значению адреса памяти 5678 и сохраните его в адресе памяти 4321, если результат положительный, либо в адрес 8765, если результат отрицательный».

Перед тем, как перейти к выполнению декодированной команды, давайте уделим немного внимания регистрам.

Регистрами называются немногочисленные, но крайне быстрые фрагменты памяти процессора. У 64-битных процессоров каждый из них вмещает 64 бита, а всего их может быть несколько десятков на одно ядро. Регистры используются для хранения используемых в данный момент значений и их можно считать чем-то вроде кэша нулевого уровня. В приведенных выше примерах команд значения А, Б и В будут сохранены именно в регистре.

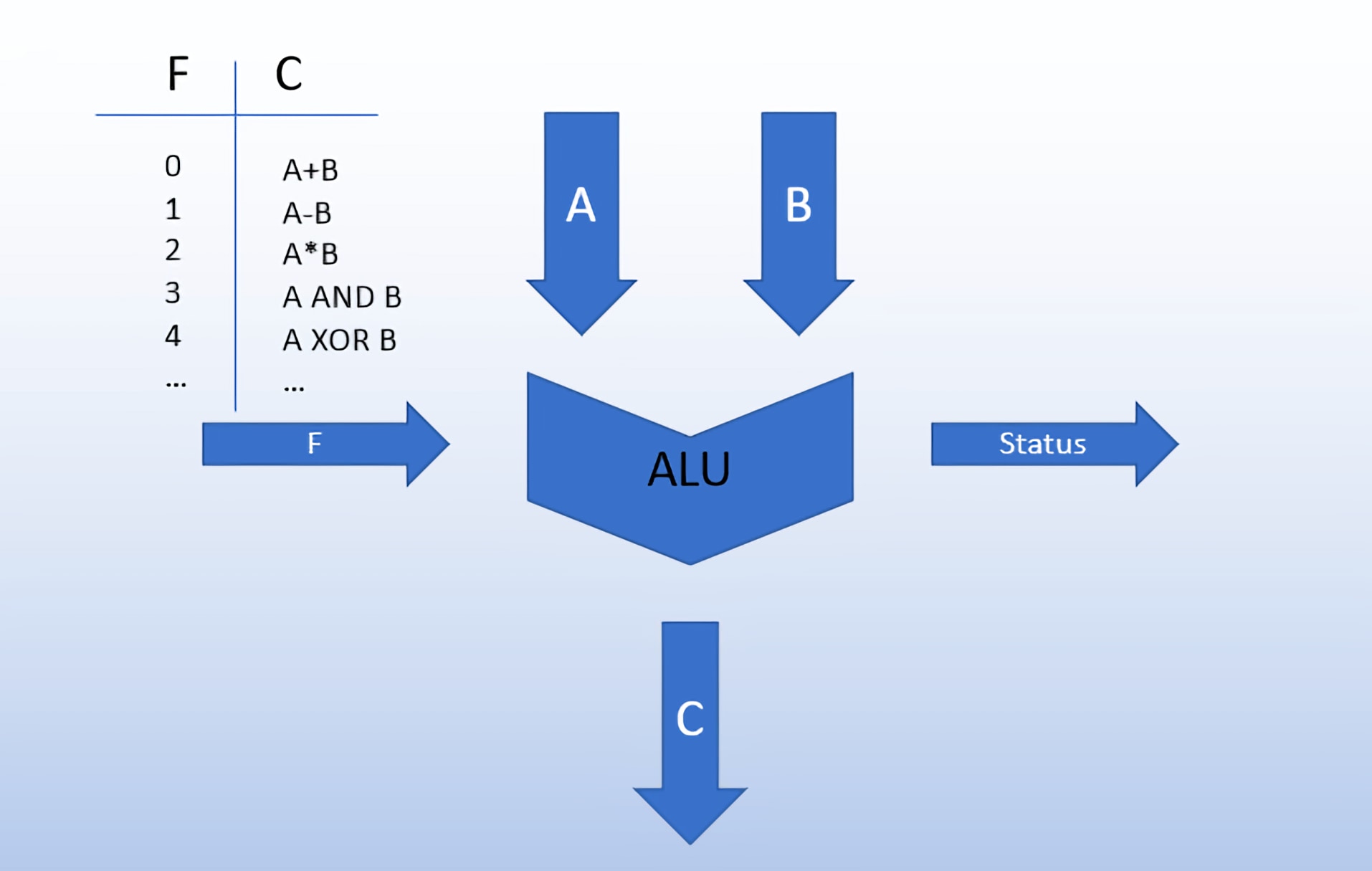

Арифметико-логическое устройство

Вернемся к этапу выполнения команд. Сразу отметим, что он отличается для всех трех вышеупомянутых типов команд, поэтому давайте рассмотрим каждый их них.

Самыми простыми для понимания являются арифметические команды. Эти команды отправляются в арифметическо-логическое устройство (ALU) для последующей обработки. Устройство представляет собой цепь, которая чаще всего работает с двумя значениями, отмеченными сигналом, и выдает результат.

Представьте себе обычный калькулятор. Для любого вычисления вы вводите значения, выбираете необходимую арифметическую операцию и получаете результат. Арифметическо-логическое устройство (ALU) работает по похожему принципу. Тип операции зависит от опкода команды, который управляющий автомат отправляет в ALU и которое в дополнение к базовой арифметике может производить со значениями такие битовые операции, как AND, OR, NOT и XOR. Кроме того, арифметическо-логическое устройство выводит информацию о проведенном вычислении для управляющего автомата (например, оказалось ли оно положительным, отрицательным, равным нулю или вызвало переполнение).

Несмотря на то, что арифметическо-логическое устройство чаще всего связано именно с арифметическими операциями, оно находит свое применение и в инструкциях памяти или перехода. Например, если процессору нужно вычислить адрес памяти, заданный в результате прошлого вычисления, либо в случае необходимости вычислить переход для добавления в счетчик программ, если инструкция того требует (пример: «если предыдущий результат отрицателен, перейти на 20 команд вперед»).

Команды и иерархия памяти

Команды перехода и ветвления

Кроме обычных команд перехода, существуют и условные переходы, с которыми процессору работать особенно сложно, поскольку он может выполнять несколько инструкций одновременно и конечный результат всей ветки может быть нельзя определить пока не начата работа над выполнением связанных команд.

Графическое представление конвейера, используемого в ядрах процессоров AMD Bobcat (2011). Обратите внимание, как много в нем различных элементов и стадий.

Процессоры используют тот же принцип для повышения пропускной способности команд. Конвейеры современных процессоров на архитектуре ARM или x86 могут использовать свыше 20 стадий вычислительного конвейера, а это значит, что ядро процессора одновременно обрабатывает свыше 20 различных команд. Процессоры могут отличаться по разделению этих стадий под различные нужды, но в одном из примеров, принцип работы которого находится в открытом доступе, имеется 4 цикла для выборки, 6 циклов для декодирования, 3 цикла для выполнения команд и 7 циклов для отправки результатов в память.

После того, как точно станет известен результат перехода (т.е. завершился конкретный этап на конвейере), счетчик команд обновится и процессор приступит к выполнению следующей операции. Если же результат не совпал с тем, который предугадал предсказатель команд, процессор сбросит все команды, которые начал выполнять по ошибке, и запустит работу с правильной точки.

Внеочередное исполнение

Теперь, когда вы знаете принцип работы трех наиболее распространенных типов команд, давайте уделим внимание более продвинутыми функциям процессоров. Практически все современные модели ЦП фактически исполняют команды не в порядке их получения. Существует такая функция, как внеочередное исполнение, призванная сократить время простоя процессора во время ожидания завершения остальных команд.

Ускорители и будущее процессоров

Конечно, процессор может делать все это самостоятельно, но созданный конкретно для этой цели блок будет намного более эффективен. Наглядным показателем мощностей ускорителей будет сравнение встроенного графического процессора с дискретной видеокартой. Разумеется, процессор может выполнять вычисления, необходимые для обработки графики, но наличие отдельного блока обеспечивает намного более высокую производительность. С ростом числа ускорителей фактическое ядро центрального процессора может занимать всего лишь небольшую часть чипа.

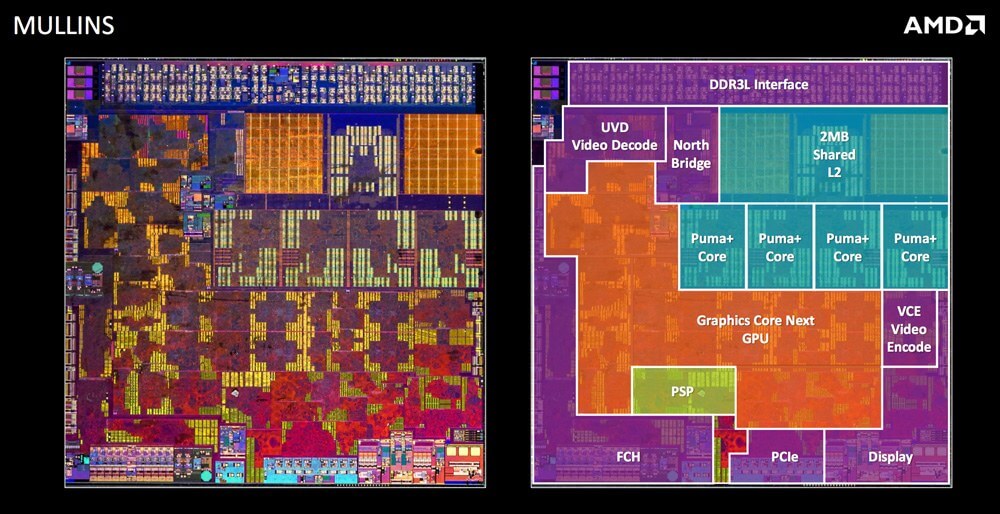

На первом рисунке снизу изображено устройство процессора Intel, выпущенного более десяти лет назад, где большая часть занята ядрами и кешем, а на втором показан гораздо более современный чип от AMD. Как мы видим, во втором случае большая часть кристалла отведена не под ядра, а под другие компоненты.

Кристалл процессора Intel первого поколения архитектуры Nehalem. Обратите внимание: ядра и кэш занимают подавляющее часть площади.

Кристалл системы на чипе от AMD. Много места отведено под ускорители и внешние интерфейсы.

Многоядерность

В случае с четырьмя ядрами процессору необходимо отправлять команды в 4 раза быстрее. Также нужно четыре раздельных интерфейса для памяти. Именно из-за наличия нескольких ядер на одном чипе, потенциально работающих с одними и теми же частями данных, возникает проблема слаженности и согласованности их работы. Предположим, если два ядра обрабатывали команду, использующую одни и те же данные, то как процессор определяет, у которого из них правильное значение? А что, если одно ядро модифицировало данные, но они не успели вовремя дойти до второго ядра? Поскольку у них есть отдельные кэши, в которых могут храниться пересекающиеся данные, для устранения возможных конфликтов необходимо использовать сложные алгоритмы и контроллеры.

Чрезвычайно важную роль в многоядерных процессорах играет и точность прогнозирования переходов. Чем больше в процессоре ядер, тем выше вероятность того, что одной из исполняемых команд будет именно команда перехода, способная в любое время изменить общий поток задач.

Физическая оболочка процессора

Несмотря на то, что большая часть этой статьи была посвящена сложным механизмам работы архитектуры процессора, не стоит забывать и о том, что все это должно быть создано и работать в виде реального, физического объекта.

Для того, чтобы синхронизировать работу всех компонентов процессора, используется тактовый сигнал. Современные процессоры обычно работают на частотах от 3.0 ГГц до 5.0 ГГц, и за последнее десятилетие ситуация особо не изменилась. При каждом цикле внутри чипа включаются и выключаются миллиарды транзисторов.

Такты важны для того, чтобы обеспечить идеальную работу каждой стадии вычислительного конвейера. Количество команд, обрабатываемых процессором за каждую секунду, зависит именно от них. Частоту можно увеличить путем разгона, сделав чип быстрее, но это в свою очередь повысит энергопотребление и тепловыделение.

Фото: Michael Dziedzic

Подытожим на примере

Чтобы подвести итоги, кратко рассмотрим архитектуру процессора Intel Core 2. Это было еще в 2006 году, поэтому некоторые детали могут быть устаревшими, но информации о новых разработках отсутствуют в публичном доступе.

На самом верху располагается кэш команд и буфер ассоциативной трансляции. Буфер помогает процессору определить, где в памяти располагаются необходимые команды. Эти инструкции хранятся в кэше команд первого уровня, а после этого отправляются в предекодер, так как из-за сложностей архитектуры x86 декодирование происходит во множество этапов. Сразу же за ними идет предсказатель переходов и предвыборщик кода, которые снижают вероятность возникновения потенциальных проблем со следующими командами.

Далее команды отправляются в очередь команд. Вспомните, как внеочередное исполнение позволяет процессору выбрать именно ту команду, которую практичнее всего выполнить в конкретный момент из очереди текущих инструкций. После того, как процессор определил нужную команду, та декодируется во множество микроопераций. В то время как команда может содержать сложную для ЦП задачу, микрооперации представляют собой детализированные задачи, которые процессору легче интерпретировать.

На самом деле, у каждого ядра процессора множество арифметическо-логических устройств и портов памяти. Команды отправляются в станцию резервации, пока не освободится устройство или порт. Затем команда обрабатывается с помощью кэша данных первого уровня, а полученный результат сохраняется для дальнейшего использования, после чего процессор может приступать к следующей задаче. На этом все!

Другие материалы по теме

Если вам хочется узнать больше о том, как создаются различные компоненты, описанные в этом тексте, то настоятельно советуем обратить внимание на вторую часть серии статей «Как разрабатываются и создаются процессоры?». Если же вы больше заинтересованы в том, как производятся физические оболочки процессоров, то вам стоит ознакомиться с третьей статьей той же серии.

Устройство и принцип работы процессора

Процессор – это основное устройство ЭВМ, выполняющее логические и арифметические операции, и осуществляющее управление всеми компонентами ЭВМ. Процессор представляет собой миниатюрную тонкую кремниевую пластинку прямоугольной формы, на которой размещается огромное количество транзисторов, реализующих все функции, выполняемые процессором. Кремневая пластинка – очень хрупкая, а так как ее любое повреждение приведет к выходу из строя процессора, то она помещается в пластиковый или керамический корпус.

Содержание.

1. Введение.

Современный процессор – это сложное и высокотехнологическое устройство, включающее в себя все самые последние достижения в области вычислительной техники и сопутствующих областей науки.

Большинство современных процессоров состоит из:

И характеризуется следующими параметрами:

Упрощенная структурная схема современного многоядерного процессора представлена на рисунке 1.

Начнем обзор устройства процессора с его основной части – ядра.

2. Ядро процессора.

Ядро процессора – это его основная часть, содержащая все функциональные блоки и осуществляющая выполнение всех логических и арифметических операций.

На рисунке 1 приведена структурная схема устройства ядра процессора. Как видно на рисунке, каждое ядро процессора состоит из нескольких функциональных блоков:

Блок выборки инструкций осуществляет считывание инструкций по адресу, указанному в счетчике команд. Обычно, за такт он считывает несколько инструкций. Количество считываемых инструкций обусловлено количеством блоков декодирования, так как необходимо на каждом такте работы максимально загрузить блоки декодирования. Для того чтобы блок выборки инструкций работал оптимально, в ядре процессора имеется предсказатель переходов.

Предсказатель переходов пытается определить, какая последовательность команд будет выполняться после совершения перехода. Это необходимо, чтобы после условного перехода максимально нагрузить конвейер ядра процессора.

Блоки декодирования, как понятно из названия, – это блоки, которые занимаются декодированием инструкций, т.е. определяют, что надо сделать процессору, и какие дополнительные данные нужны для выполнения инструкции. Задача эта для большинства современных коммерческих процессоров, построенных на базе концепции CISC, – очень сложная. Дело в том, что длина инструкций и количество операндов – нефиксированные, и это сильно усложняет жизнь разработчикам процессоров и делает процесс декодирования нетривиальной задачей.

Часто отдельные сложные команды приходится заменять микрокодом – серией простых инструкций, в совокупности выполняющих то же действие, что и одна сложная инструкция. Набор микрокода прошит в ПЗУ, встроенном в процессоре. К тому же микрокод упрощает разработку процессора, так как отпадает надобность в создании сложноустроенных блоков ядра для выполнения отдельных команд, да и исправить микрокод гораздо проще, чем устранить ошибку в функционировании блока.

В современных процессорах, обычно, бывает 2-4 блока декодирования инструкций, например, в процессорах Intel Core 2 каждое ядро содержит по два таких блока.

Блоки выборки данных осуществляют выборку данных из КЭШ-памяти или ОЗУ, необходимых для выполнения текущих инструкций. Обычно, каждое процессорное ядро содержит несколько блоков выборки данных. Например, в процессорах Intel Core используется по два блока выборки данных для каждого ядра.

Управляющий блок на основании декодированных инструкций управляет работой блоков выполнения инструкций, распределяет нагрузку между ними, обеспечивает своевременное и верное выполнение инструкций. Это один из наиболее важных блоков ядра процессора.

Блоки выполнения инструкций включают в себя несколько разнотипных блоков:

ALU – арифметическое логическое устройство;

FPU – устройство по выполнению операций с плавающей точкой;

Блоки для обработки расширения наборов инструкций. Дополнительные инструкции используются для ускорения обработки потоков данных, шифрования и дешифрования, кодирования видео и так далее. Для этого в ядро процессора вводят дополнительные регистры и наборы логики. На данный момент наиболее популярными расширениями наборов инструкция являются:

MMX (Multimedia Extensions) – набор инструкций, разработанный компанией Intel, для ускорения кодирования и декодирования потоковых аудио и видео-данных;

SSE (Streaming SIMD Extensions) – набор инструкций, разработанный компанией Intel, для выполнения одной и той же последовательности операций над множеством данных с распараллеливанием вычислительного процесса. Наборы команд постоянно совершенствуются, и на данный момент имеются ревизии: SSE, SSE2, SSE3, SSSE3, SSE4;

ATA (Application Targeted Accelerator) – набор инструкций, разработанный компанией Intel, для ускорения работы специализированного программного обеспечения и снижения энергопотребления при работе с такими программами. Эти инструкции могут использоваться, например, при расчете контрольных сумм или поиска данных;

3DNow – набор инструкций, разработанный компанией AMD, для расширения возможностей набора инструкций MMX;

AES (Advanced Encryption Standard) – набор инструкций, разработанный компанией Intel, для ускорения работы приложений, использующих шифрование данных по одноименному алгоритму.

Блок сохранения результатов обеспечивает запись результата выполнения инструкции в ОЗУ по адресу, указанному в обрабатываемой инструкции.

Блок работы с прерываниями. Работа с прерываниями – одна из важнейших задач процессора, позволяющая ему своевременно реагировать на события, прерывать ход работы программы и выполнять требуемые от него действия. Благодаря наличию прерываний, процессор способен к псевдопараллельной работе, т.е. к, так называемой, многозадачности.

Обработка прерываний происходит следующим образом. Процессор перед началом каждого цикла работы проверяет наличие запроса на прерывание. Если есть прерывание для обработки, процессор сохраняет в стек адрес инструкции, которую он должен был выполнить, и данные, полученные после выполнения последней инструкции, и переходит к выполнению функции обработки прерывания.

После окончания выполнения функции обработки прерывания, из стека считываются сохраненные в него данные, и процессор возобновляет выполнение восстановленной задачи.

Регистры – сверхбыстрая оперативная память (доступ к регистрам в несколько раз быстрее доступа к КЭШ-памяти) небольшого объема (несколько сотен байт), входящая в состав процессора, для временного хранения промежуточных результатов выполнения инструкций. Регистры процессора делятся на два типа: регистры общего назначения и специальные регистры.

Регистры общего назначения используются при выполнении арифметических и логических операций, или специфических операций дополнительных наборов инструкций (MMX, SSE и т.д.).

Регистры специального назначения содержат системные данные, необходимые для работы процессора. К таким регистрам относятся, например, регистры управления, регистры системных адресов, регистры отладки и т.д. Доступ к этим регистрам жестко регламентирован.

Счетчик команд – регистр, содержащий адрес команды, которую процессор начнет выполнять на следующем такте работы.

2.1 Принцип работы ядра процессора.

Принцип работы ядра процессора основан на цикле, описанном еще Джоном фон Нейманом в 1946 году. В упрощенном виде этапы цикла работы ядра процессора можно представить следующим образом:

1. Блок выборки инструкций проверяет наличие прерываний. Если прерывание есть, то данные регистров и счетчика команд заносятся в стек, а в счетчик команд заносится адрес команды обработчика прерываний. По окончанию работы функции обработки прерываний, данные из стека будут восстановлены;

2. Блок выборки инструкций из счетчика команд считывает адрес команды, предназначенной для выполнения. По этому адресу из КЭШ-памяти или ОЗУ считывается команда. Полученные данные передаются в блок декодирования;

3. Блок декодирования команд расшифровывает команду, при необходимости используя для интерпретации команды записанный в ПЗУ микрокод. Если это команда перехода, то в счетчик команд записывается адрес перехода и управление передается в блок выборки инструкций (пункт 1), иначе счетчик команд увеличивается на размер команды (для процессора с длинной команды 32 бита – на 4) и передает управление в блок выборки данных;

4. Блок выборки данных считывает из КЭШ-памяти или ОЗУ требуемые для выполнения команды данные и передает управление планировщику;

5. Управляющий блок определяет, какому блоку выполнения инструкций обработать текущую задачу, и передает управление этому блоку;

6. Блоки выполнения инструкций выполняют требуемые командой действия и передают управление блоку сохранения результатов;

7. При необходимости сохранения результатов в ОЗУ, блок сохранения результатов выполняет требуемые для этого действия и передает управление блоку выборки инструкций (пункт 1).

Описанный выше цикл называется процессом (именно поэтому процессор называется процессором). Последовательность выполняемых команд называется программой.

Скорость перехода от одного этапа цикла к другому определяется тактовой частотой процессора, а время работы каждого этапа цикла и время, затрачиваемое на полное выполнение одной инструкции, определяется устройством ядра процессора.

2.2. Способы повышения производительности ядра процессора.

Увеличение производительности ядра процессора, за счет поднятия тактовый частоты, имеет жесткое ограничение. Увеличение тактовой частоты влечет за собой повышение температуры процессора, энергопотребления и снижение стабильности его работы и срока службы.

Поэтому разработчики процессоров применяют различные архитектурные решения, позволяющие увеличить производительность процессоров без увеличения тактовой частоты.

Рассмотрим основные способы повышения производительности процессоров.

2.2.1. Конвейеризация.

Каждая инструкция, выполняемая процессором, последовательно проходит все блоки ядра, в каждом из которых совершается своя часть действий, необходимых для выполнения инструкции. Если приступать к обработке новой инструкции только после завершения работы над первой инструкцией, то большая часть блоков ядра процессора в каждый момент времени будет простаивать, а, следовательно, возможности процессора будут использоваться не полностью.

Рассмотрим пример, в котором процессор будет выполнять программу, состоящую из пяти инструкций (К1–К5), без использования принципа конвейеризации. Для упрощения примера примем, что каждый блок ядра процессора выполняет инструкцию за 1 такт.

| Такты | Выборка инструкции | Декодирование инструкции | Выборка данных | Выполнение инструкции | Сохранение результата |

| 1 | K1 | — | — | — | — |

| 2 | — | K1 | — | — | — |

| 3 | — | — | K1 | — | — |

| 4 | — | — | — | K1 | — |

| 5 | — | — | — | — | K1 |

| 6 | K2 | — | — | — | — |

| 7 | — | K2 | — | — | — |

| 8 | — | — | K2 | — | — |

| 9 | — | — | — | K2 | — |

| 10 | — | — | — | — | K2 |

| 11 | K3 | — | — | — | — |

| 12 | — | K3 | — | — | — |

| 13 | — | — | K3 | — | — |

| 14 | — | — | — | K3 | — |

| 15 | — | — | — | — | K3 |

| 16 | K4 | — | — | — | — |

| 17 | — | K4 | — | — | — |

| 18 | — | — | K4 | — | — |

| 19 | — | — | — | K4 | — |

| 20 | — | — | — | — | K4 |

| 21 | K5 | — | — | — | — |

| 22 | — | K5 | — | — | — |

| 23 | — | — | K5 | — | — |

| 24 | — | — | — | K5 | — |

| 25 | — | — | — | — | K5 |

Как видно из таблицы, для выполнения пяти инструкций процессору понадобилось 25 тактов. При этом в каждом такте четыре из пяти блоков ядра процессора простаивали, т.е. процессор использовал всего 20% своего потенциала. Естественно, в реальных процессорах все сложнее. Разные блоки процессора решают разные по сложности задачи. Сами инструкции тоже отличаются друг от друга по сложности. Но в общем ситуация остается такой же.

Для решения этой проблемы во всех современных процессорах выполнение инструкций построено по принципу конвейера, то есть по мере освобождения блоков ядра, они загружаются обработкой следующей инструкции, не дожидаясь пока предыдущая инструкция выполнится полностью.

Рассмотрим пример выполнения той же программы, состоящей из пяти инструкций, но с использованием принципа конвейеризации.

| Такты | Выборка инструкции | Декодирование инструкции | Выборка данных | Выполнение инструкции | Сохранение результата |

| 1 | K1 | — | — | — | — |

| 2 | K2 | K1 | — | — | — |

| 3 | K3 | K2 | K1 | — | — |

| 4 | K4 | K3 | K2 | K1 | — |

| 5 | K5 | K4 | K3 | K2 | K1 |

| 6 | — | K5 | K4 | K3 | K2 |

| 7 | — | — | K5 | K4 | K3 |

| 8 | — | — | — | K5 | K4 |

| 9 | — | — | — | — | K5 |

Та же программа была выполнена за 9 тактов, что почти 2.8 раза быстрее, чем при работе без конвейера. Как видно из таблицы максимальная загрузка процессора была получена на 5 такте. В этот момент использовались все блоки ядра процессора. А с первого по четвертый такт, включительно, происходило наполнение конвейера.

Так как процессор выполняет команды непрерывно, то, в идеале, он мог бы быть занят на 100%, при этом, чем длиннее был бы конвейер, тем больший выигрыш в производительности был бы получен. Но на практике это не так.

Во-первых, реальный поток команд, обрабатываемый процессором – непоследовательный. В нем часто встречаются переходы. При этом пока команда условного перехода не будет обработана полностью, конвейер не сможет начать выполнение новой команды, так как не знает, по какому адресу она находится.

После условного перехода конвейер приходится наполнять заново. И чем длиннее конвейер, тем дольше это происходит. В результате, прирост производительности от введения конвейера снижается.

Для уменьшения влияния условных переходов на работу конвейера, в ядро процессора вводятся блоки предсказания условных переходов. Основная задача этих блоков – определить, когда будет совершен условный переход и какие команды будут выполнены после совершения условного перехода.

Если условный переход удалось предсказать, то выполнение инструкций по новому адресу начинается раньше, чем будет закончена обработка команды условного перехода. В результате, наполнение конвейера не пострадает.

По статистике, точность блоков предсказания условных переходов в современных процессорах превышает 90%, что позволяет делать достаточно длинные, но при этом хорошо наполняемые конвейеры.

Во-вторых, часто обрабатываемые инструкции – взаимосвязаны, то есть одна из инструкций требует в качестве исходных данных результата выполнения другой инструкции.

В этом случае она может быть выполнена только после полного завершения обработки первой инструкции. Однако современные процессоры могут анализировать код на несколько инструкций вперед и, например, параллельно с первой инструкцией обработать третью инструкцию, которая никак не зависит от первых двух.

В большинстве современных процессорах задача анализа взаимосвязи инструкций и составления порядка их обработки ложится на плечи процессора, что неминуемо ведет к снижению его быстродействия и увеличению стоимости.

Однако все большую популярность получает статическое планирование, когда порядок выполнения программы процессором определяется на этапе компиляции программы. В этом случае инструкции, которые можно выполнить параллельно, объединяются компилятором в одну длинную команду, в которой все инструкции заведомо параллельны. Процессоры, работающие с такими инструкциями, построены на базе архитектура VLIW (Very long instruction word).

2.2.2. Суперскалярность.

Суперскалярность – архитектура вычислительного ядра, при которой наиболее нагруженные блоки могут входить в нескольких экземплярах. Скажем, в ядре процессора блок выборки инструкций может нагружать сразу несколько блоков декодирования.

В этом случае блоки, выполняющие более сложные действия и работающие дольше, за счет параллельной обработки сразу нескольких инструкций не будут задерживать весь конвейер.

Однако параллельное выполнение инструкций возможно, только если эти инструкции – независимые.

Структурная схема ядра конвейера гипотетического процессора, построенного с использованием принципа суперскалярности, приведена на рисунке 1. На этом рисунке в каждом ядре процессора работает несколько блоков декодирования, несколько блоков выборки данных и несколько блоков выполнения инструкций.

2.2.3. Параллельная обработка данных.

Бесконечно повышать производительность процессоров, за счет увеличения тактовой частоты, невозможно. Увеличение тактовой частоты влечет за собой увеличение тепловыделения, уменьшение срока службы и надежности работы процессоров, да и задержки от обращения к памяти сильно снижают эффект от увеличения тактовой частоты. Действительно, сейчас практически не встретишь процессоры с тактовой частотой выше 3.8 ГГц.

Связанные с увеличением тактовой частоты проблемы заставляют разработчиков искать иные пути повышения производительности процессоров. Один из наиболее популярных способов – параллельные вычисления.

Подавляющее большинство современных процессоров имеют два и более ядра. Топовые модели могут содержать и 8, и даже 12 ядер, причем с поддержкой технологии hyper-threading. Преимущества от ввода дополнительных ядер вполне понятны, мы практически получаем несколько процессоров, способных независимо решать каждый свои задачи, при этом, естественно, возрастает производительность. Однако прирост производительности далеко не всегда оправдывает ожидания.

Во-первых, далеко не все программы поддерживают распределение вычислений на несколько ядер. Естественно, можно программы разделять между ядрами, чтобы на каждом ядре работал свой набор независимых программ. Например, на одном ядре работает операционная система с набором служебных программ, на другом пользовательские программы и так далее.

Но это дает выигрыш в производительности до тех пор, пока не появляется программа, требующая ресурсов больше, чем может дать одно ядро. Хорошо, если она поддерживает распределение нагрузки между несколькими ядрами. Но на данный момент общедоступных программ, способных распределить нагрузку между 12 ядрам, да еще в режиме Hyper-Threading, можно «сосчитать на пальцах одной руки». Я, конечно, утрирую, существуют программы, оптимизированные для многопоточных вычислений, но большинству простых пользователей они не нужны. А вот наиболее популярные программы, а тем более игры, пока что «плохо» адаптируются к многоядерным процессорам, особенно, если количество ядер больше четырех.

Во-вторых, усложняется работа с памятью, так как ядер – много, и всем им требуется доступ к ОЗУ. Требуется сложный механизм, определяющий очередность доступа ядер процессора к памяти и к другим ресурсам ЭВМ.

В-третьих, возрастает энергопотребление, а, следовательно, увеличивается тепловыделение и требуется мощная система охлаждения.

Ну и, в-четвертых, себестоимость производства многоядерных процессоров – немаленькая, а, соответственно, и цена на такие процессоры «кусается».

Несмотря на все недостатки, применение процессоров с 2-4 ядрами, несомненно, дает значительный прирост производительности. Однако, на данный момент, применение процессоров с количеством ядер больше четырех не всегда оправдывает ожидание. Однако, в ближайшем будущем, ситуация должна кардинально измениться. Обязательно появится множество программ с поддержкой многопоточности, производительность отдельных ядер возрастет, а их цена снизится.

2.2.4. Технология Hyper-Threading.

Технология Intel Hyper-threading позволяет каждому ядру процессора выполнять две задачи одновременно, по сути, делая из одного реального ядра два виртуальных. Это возможно из-за того, что в таких ядрах сохраняется состояние сразу двух потоков, так как у ядра есть свой набор регистров, свой счетчик команд и свой блок работы с прерываниями для каждого потока. В результате, операционная система видит такое ядро, как два отдельных ядра, и будет с ними работать так же, как работала бы с двуядерным процессором.

Однако остальные элементы ядра для обоих потоков – общие, и делятся между ними. Кроме этого, когда по какой-либо причине один из потоков освобождает элементы конвейера, другой поток использует свободные блоки.

Элементы конвейера могут быть не задействованы, если, например, произошел промах при обращении в КЭШ-память, и необходимо считать данные из ОЗУ, или неверно был предсказан переход, или ожидаются результаты обработки текущей инструкции, или какие-то блоки вообще не используются при обработке данной инструкции и т.д.

Большинство программ не могут полностью нагрузить процессор, так как некоторые, в основном, используют несложные целочисленные вычисления, практически не задействуя блок FPU. Другие же программы, например 3D-студия, требуют массу расчетов с использованием чисел с плавающей точкой, но при этом освобождая некоторые другие исполнительные блоки и так далее.

К тому же практически во всех программах – много условных переходов и зависимых переменных. В результате, использование технологии Hyper-threading может дать существенный прирост производительности, способствуя максимальной загрузке конвейера ядра.

Но не все так просто. Естественно, прирост производительности будет меньше, чем от использования нескольких физических ядер, так как все-таки потоки используют общие блоки одного конвейера и часто вынуждены ждать освобождения требуемого блока. К тому же большинство процессоров уже имеют несколько физических ядер, и при использовании технологии Hyper-threading виртуальных ядер может стать слишком много, особенно, если процессор содержит четыре и больше физических ядра.

Так как на данный момент программ, способных распределять вычисления на большое количество ядер, – крайне мало, то в этом случае результат может разочаровать пользователей.

Есть еще одна серьезная проблема технологии Hyper-Threading – это конфликты, возникающие, когда инструкции разных потоков нуждаются в однотипных блоках. Может сложиться ситуация, когда параллельно будут работать два схожих потока, часто использующие одни и те же блоки. В таком случае прирост производительности будет минимален.

В результате, технология Hyper-Threading очень зависима от типа нагрузки на процессор и может дать хороший прирост производительности, а может быть практически бесполезной.

2.2.5. Технология Turbo Boost.

Производительность большинства современных процессоров в домашних условиях можно немного поднять, попросту говоря разогнать – заставить работать на частотах, превышающих номинальную, т.е. заявленную производителем.

Частота процессора рассчитывается, как частота системной шины, умноженная на некий коэффициент, называемый множителем. Например, процессор Core i7-970 работает с системной шиной DMI на базовой частоте – 133 МГц, и имеет множитель – 24. Таким образом, тактовая частота ядра процессора составит: 133 Мгц*24= 3192 Мгц.

Если в настройках BIOS увеличить множитель или поднять тактовую частоту системной шины, то тактовая частота процессора увеличится, а, соответственно, увеличится и его производительность. Однако процесс этот – далеко небезопасный. Из-за разгона процессор может работать нестабильно или вообще выйти из строя. Поэтому к разгону нужно подходить ответственно и тщательно контролировать параметры работы процессора.

С появление технологии Turbo Boost все стало гораздо проще. Процессоры с этой технологией могут сами динамически, на короткий промежуток времени, повышать тактовую частоту, тем самым, увеличивая свою производительность. При этом процессор контролирует все параметры своей работы: напряжение, силу тока, температуру и т.д., не допуская сбоев и тем более выхода из строя. Например, процессор может отключить неиспользуемые ядра, тем самым, понизив общую температуру, а взамен увеличить тактовую частоту остальных ядер.

Так как на данный момент существует не очень много программ, использующих для обработки данных все процессорные ядра, особенно, если их больше четырех, то применение технологии Turbo Boost позволяет значительно поднять производительность процессора, особенно, при работе с однопоточными приложениями.

2.2.6. Эффективность выполнения команд.

В зависимости от типов обрабатываемых инструкций и способа их исполнения, процессоры подразделяются на несколько групп:

CISC (Complex instruction set computer) – это процессоры со сложным набором команд. Архитектура CISC характеризуется:

Исторически, процессоры с архитектурой CISC появились первыми, и их появление было обусловлено общей тенденцией разработки первых ЭВМ. ЭВМ стремились сделать более функциональными и в то же время простыми для программирования. Естественно, для программистов вначале было удобнее иметь широкий набор команд, чем реализовывать каждую функцию целой отдельной подпрограммой. В результате, объем программ сильно сокращался, а вместе с ним и трудоемкость программирования.

Однако такая ситуация продолжалась недолго. Во-первых, с появлением языков высокого уровня отпала необходимость непосредственного программирования в машинных кодах и на ассемблере, и, во-вторых, со временем количество различных команд сильно выросло, а сами инструкции усложнились. В результате, большинство программистов, в основном, использовали какой-то определенный набор инструкций, практически игнорируя наиболее сложные инструкции.

В результате, программисты уже не имели особой выгоды от широкого набора инструкций, так как компиляция программ стала автоматической, а сами процессоры обрабатывали сложные и разнообразные инструкции медленно, в основном, из-за проблем с их декодированием.

К тому же новые сложные инструкции разработчики процессоров отлаживали меньше, так как это был трудоемкий и сложный процесс. В результате, некоторые из них могли содержать ошибки.

Ну и, естественно, чем сложнее инструкции, чем больше действий они выполняют, тем сложнее их выполнение распараллеливать, и, соответственно, тем менее эффективно они загружают конвейер процессора.

Однако к этому моменту уже было разработано огромное количество программ для процессоров с CISC архитектурой, поэтому экономически было невыгодно переходить на принципиально новую архитектуру, даже дающую выигрыш в производительности процессора.

Поэтому был принят компромисс, и CISC процессоры, начиная с Intel486DX, стали производить с использованием RISC-ядра. Т.е., непосредственно перед исполнением, сложные CISC-инструкции преобразуют в более простой набор внутренних инструкций RISC. Для этого используют записанные в размещенном внутри ядра процессора ПЗУ наборы микрокоманд – серии простых инструкций, в совокупности выполняющих те же действия, что и одна сложная инструкция.

RISC (Reduced Instruction Set Computer) – процессоры с сокращенным набором инструкций.

В концепции RISC-процессоров предпочтение отдается коротким, простым и стандартизированным инструкциям. В результате, такие инструкции проще декодировать и выполнять, а, следовательно, устройство процессора становится так же проще, так как не требуется сложных блоков для выполнения нестандартных и многофункциональных инструкций. В результате, процессор становится дешевле, и появляется возможность дополнительно поднять его тактовую частоту, за счет упрощения внутренней структуры и уменьшения количества транзисторов, или снизить энергопотребление.

Так же простые RISC-инструкции гораздо проще распараллеливать, чем CISC-инструкции, а, следовательно, появляется возможность больше загрузить конвейер, ввести дополнительные блоки обработки инструкций и т.д.

Процессоры, построенные по архитектуре RISC, обладают следующими основными особенностями:

В результате, хотя RISC-процессоры и требуют выполнения большего количества инструкций для решения одной и той же задачи, по сравнению с CISС-процессорами, они, в общем случае, показывают более высокую производительность. Во-первых, выполнение одной RISC-инструкции занимает гораздо меньше времени, чем выполнение CISC-инструкции. Во-вторых, RISC-процессоры более широко используют возможности параллельной работы. В-третьих, RISC-процессоры могут иметь более высокую тактовую частоту, по сравнению с CISC-процессорами.

В результате, экономически крайне невыгодно переписывать все программы, которые уже разработаны, отлажены и используются огромным количеством пользователей. Вот так и получилось, что теперь мы вынуждены использовать CISC-процессоры. Правда, как я уже говорил, разработчики нашли компромиссное решение данной проблемы, и уже очень давно в CISC-процессорах используют RISC-ядро и замену сложных команд на микропрограммы. Это позволило несколько сгладить ситуацию. Но все же RISC-процессоры по большинству параметров выигрывают даже у CISC-процессоров с RISC-ядром.

MISC (Minimal Instruction Set Computer) – дальнейшее развитие архитектуры RISС, основанное на еще большем упрощении инструкций и уменьшении их количества. Так, в среднем, в MISC-процессорах используется 20-30 простых инструкций. Такой подход позволил еще больше упростить устройство процессора, снизить энергопотребление и максимально использовать возможности параллельной обработки данных.

VLIW (Very long instruction word) – архитектура процессоров, использующая инструкции большой длины, содержащие сразу несколько операций, объединенных компилятором для параллельной обработки. В некоторых реализациях процессоров длина инструкций может достигать 128 или даже 256 бит.

Архитектура VLIW является дальнейшим усовершенствованием архитектуры RISC и MISC с углубленным параллелизмом.

Если в процессорах RISC организацией параллельной обработки данных занимался сам процессор, при этом, затрачивая часть ресурсов на анализ инструкций, выявление зависимостей и предсказание условных переходов (причем, зачастую, процессор мог ошибаться, например, в предсказании условных переходов, тем самым внося серьезные задержки в обработку инструкций, или просматривать код программы на недостаточную глубину для выявления независимых операций, которые могли бы выполняться параллельно), то в VLIW-процессорах задача оптимизации параллельной работы возлагалась на компилятор, который не был ограничен ни во времени, ни в ресурсах и мог проанализировать всю программу для составления оптимального для работы процессора кода.

В результате, процессор VLIW выигрывал не только от упразднения накладных расходов на организацию параллельной обработки данных, но и получал прирост производительности, из-за более оптимальной организации параллельного выполнения инструкций.

Кроме этого упрощалась конструкция процессора, так как упрощались или вовсе упразднялись некоторые блоки, отвечающие за анализ зависимостей и организацию распараллеливания обработки инструкций, а это, в свою очередь, вело к снижению энергопотребления и себестоимости процессоров.

Однако даже компилятору тяжело справляться с анализом кода и организацией его распараллеливания. Часто код программы был сильно взаимозависимый, и, в результате, в инструкции компилятору приходилось вставлять пустые команды. Из-за этого программы для VLIW-процессоров могли быть гораздо длиннее, чем аналогичные программы для традиционных архитектур.

Первые VLIW-процессоры появились в конце 1980-х годов и были разработаны компанией Cydrome. Так же к процессорам с этой архитектурой относятся процессоры TriMedia фирмы Philips, семейство DSP C6000 фирмы Texas Instruments, Эльбру?с 2000 – процессор российского производства, разработанный компанией МЦСТ при участии студентов МФТИ и др. Поддержка длинных инструкций с явным параллелизмом есть и в процессорах семейства Itanium.

2.3. Способы снижения энергопотребления процессора.

Не менее, чем производительность, для процессора важен и такой параметр, как энергопотребление. Особенно остро вопрос энергопотребления встал сейчас, когда наблюдается настоящий бум популярности портативных устройств.

Нашу жизнь уже нельзя представить комфортной без использования ноутбуков, планшетных компьютеров и смартфонов. Однако единственное, что омрачает эту тенденцию, – это время автономной работы подобных устройств. Так ноутбуки, в среднем, могут автономно работать 3-5 часов, планшеты – чуть больше, смартфоны уже могут протянуть при полной нагрузке почти сутки и то не все. Но все это крайне мало для комфортной работы с ними.

Время автономной работы этих устройств напрямую зависит от их энергопотребления, и немалая доля энергопотребления приходится на процессор. Для снижения энергопотребления процессоров используются различные способы и технологии. Давайте рассмотрим наиболее популярные из них.

Самый простой способ снизить энергопотребление и тепловыделение процессора – это уменьшить его тактовую частоту и напряжение, так как энергопотребление процессора пропорционально квадрату его рабочего напряжения и пропорционально тактовой частоте. Наиболее выгодно на энергопотреблении сказывается снижение напряжения. Однако при понижении напряжения рано или поздно уменьшается и тактовая частота, что естественно повлечет за собой снижение производительности.

Однако, зачастую, энергопотребление бывает более критическим параметром работы, и некоторое снижение производительности допустимо. Так большинство мобильных версий процессоров и процессоров для встраиваемых систем имеют тактовую частоту и рабочее напряжение гораздо ниже, чем у их собратьев для настольных версий.

Но не всегда производители устанавливают оптимальное сочетание напряжения и тактовой частоты. Многие мобильные процессоры с установленной тактовой частотой могли бы работать с более низким напряжением, что позволило бы существенно продлить время автономной работы портативного компьютера.

Для получения оптимального соотношения производительности к энергопотреблению, необходимо подобрать такое напряжение, при котором на заданной тактовой частоте процессор будет стабильно работать.

Тактовая частота определяется, исходя из потребностей пользователя, затем для нее подбирается минимальное рабочее напряжение путем постепенного снижения напряжения и тестирования процессора под нагрузкой.

Существуют и не столь кардинальные пути решения этой проблемы.

Например, технология EIST (Enhanced Intel SpeedStep Technology) позволяет динамически изменять энергопотребление процессора, за счет изменения тактовой частоты процессора и напряжения. Изменение тактовой частоты происходит, за счет уменьшения или увеличения коэффициента умножения.

О коэффициенте умножения я уже упоминал выше, но повторюсь. Тактовая частота процессора рассчитывается, как тактовая частота системной шины, умноженная на некий коэффициент, называемый коэффициентом умножения. Уменьшение или увеличение этого коэффициента ведет к уменьшению или увеличению тактовой частоты процессора и к снижению или увеличению рабочего напряжения.

В случаях, когда процессор используется не полностью, его тактовую частоту можно снизить, уменьшая коэффициент умножения. Как только пользователю потребуется больше вычислительных ресурсов, коэффициент умножения будет повышен, вплоть до своего номинального значения. Таким образом, удается несколько снизить энергопотребление.