Ram это какая память

Ram это какая память

Что такое RAM и ROM-память?

Все смартфоны имеют определенный объем памяти, и это один из ключевых моментов, который вы должны учитывать при покупке нового телефона.

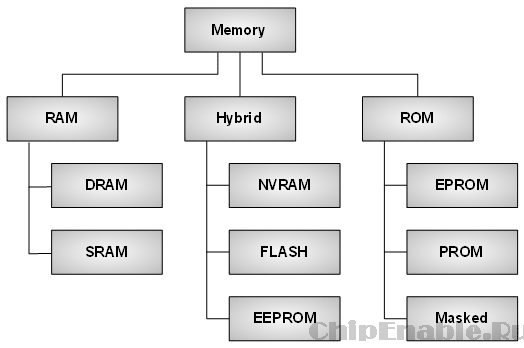

Существует два вида памяти: RAM (оперативная) и ROM (постоянная, внутренняя). RAM-память, как правило, имеет меньший объем, а назначение ее состоит в том, чтобы хранить информацию, обрабатываемую процессором.

ROM-память относится к категории долговременной памяти, и в ней можно установить всю операционную систему, а также приложения и различные файлы.

Итак, давайте рассмотрим подробнее эти два вида памяти.

Что такое RAM?

Чтобы понять, что такое оперативная память, вам нужно узнать, что обозначает аббревиатура «RAM». В переводе с английского это значит «Память с произвольным доступом», или также «Оперативное запоминающее устройство» (ОЗУ). Говоря иначе, информация в такой памяти может быть прочитана и записана в любой момент, без необходимости ожидания выполнения ряда процессов.

Это значительно ускоряет поиск тех или иных данных, так как, в отличие от ROM-памяти или памяти формата microSD, можно быстро получить доступ к физическому местоположению, где хранится данные.

Особенности RAM-памяти

Оперативная память – это то место, которое любое устройство использует для заполнения какими-либо данными, например, операционная система, приложения, используемые по прямому назначению и те, которые работают в фоновом режиме. RAM – это хранилище, откуда процессор получает всю необходимую информацию напрямую.

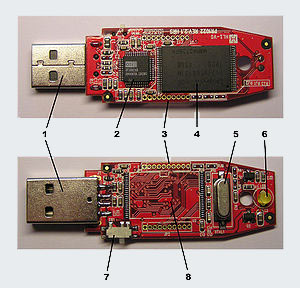

Вот поэтому ОЗУ и процессор располагаются на единой платформе-модуле, которая припаяна к материнской плате. На изображении ниже вы можете увидеть материнскую плату Nexus 5X. Этот девайс имеет оперативную память на 2 гигабайта, процессор, отмеченный красным цветом, и внутреннюю память с оранжевой отметкой.

Чем больший объем RAM-памяти присутствует в вашем телефоне, тем лучше производительность и скорость работы девайса в целом, хотя это также зависит от типа памяти и качества сборки телефона.

Важный момент: оперативная память работает только тогда, когда устройство включено – то есть, такой тип памяти не способен хранить информацию после выключения девайса. Вот поэтому имеется небольшая задержка при включении смартфона, во время которой оперативная память подготавливается для работы с ОС устройства.

Виды оперативной памяти

На сегодняшний день существует множество видов RAM-памяти, которые различаются между собой по скорости чтения и потребляемой мощности. Самые первые сообщения об оперативной памяти появились в 60-х годах прошлого столетия, и с тех пор каждое новое поколение ОЗУ характеризовалось большей емкостью, скоростью и энергоэффективностью.

В наши дни в смартфонах используется особый вид RAM-памяти, называемый LPDDR. Такая память расходует очень мало энергии, с одной стороны, но с другой, она недешева. Наиболее распространены такие виды ОЗУ: LPDDR2, LPDDR3 и LPDDR4 – это последние три поколения оперативной памяти для мобильных устройств. Главное различие между ними состоит в том, что у каждого последующего поколения наблюдается удвоение скорости передачи данных.

Что такое ROM?

Если RAM – это память уровня «чтение-запись», то ROM является памятью, рассчитанной лишь для сохранения информации. Аббревиатура «ROM» переводится на русский как «Память, доступная лишь для чтения» (отечественный вариант – «Постоянное запоминающее устройство» (ПЗУ). Данные, хранящиеся в такой памяти, не могут быть изменены – по крайней мере, сделать это не так легко или быстро.

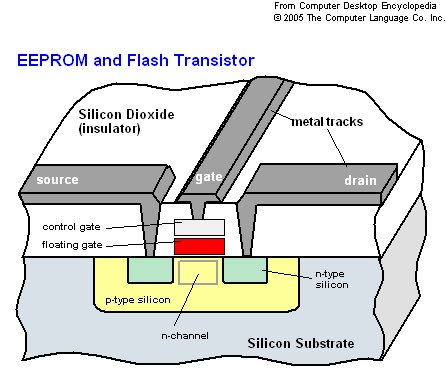

В более новых поколениях ПЗУ, таких как EPROM или Flash EEPROM (флеш-память), содержимое может быть удалено и перезаписано большое количество раз, но такая память по-прежнему считается «только для чтения». Основная причина этого заключается в том, что процесс стирания и записи относительно медленный, и он может быть использован лишь для мест, подвергнувшихся процессу форматирования.

Сегодня ROM-память в смартфонах намного быстрее, чем жесткие диски обычных ПК, а модули с данным видом памяти также монтируются непосредественно на материнской плате. В этом виде памяти хранится особная программа-загрузчик, которая запускает устройство и загружает операционную систему, а также сама ОС, все приложения и пользовательские данные.

Как правило, модифицированные версии операционной системы также относятся к ROM-памяти (такие версии еще называют «пользовательские прошивки ОС»). Быстрый поиск онлайн скажет вам, что существует множество вариантов пользовательских прошивок. Такие прошивки именуются «ROM» потому, что каждая из них представляет собой образ системы, подобный тому, который записан в ROM-память заводом-изготовителем.

Была ли наша статья полезной для вас? Что вам было бы еще интересно узнать на эту тему? Поделитесь с нами вашими мыслями в комментариях.

Что такое ОЗУ или RAM в телефонах и смартфонах

Изучая технические характеристики телефонов и смартфонов, пользователи часто задаются вопросом, что такое ОЗУ или RAM и на что оно влияет. Если вас также интересуют эти вопросы, то предлагаем вам ознакомиться с данной статьей.

Что такое ОЗУ или RAM

Что касается аббревиатуры RAM, то она расшифровывается как Random Access Memory и также обозначает оперативную память. Все эти термины означают одно и тоже – оперативную память. Поэтому если в характеристиках телефона или смартфона указано «RAM 2 Gb» или «ОЗУ 2 Гб», то это означает, что объем оперативной памяти данного мобильного устройства составляет 2 Гигабайта.

Также в характеристиках телефонов или смартфонов можно встретить такие аббревиатуры как ПЗУ или ROM (вариант ROM используется редко). ПЗУ – это Постоянное запоминающее устройство, а ROM – это Read-only memory. Этими терминами обозначают постоянную память смартфона (ее еще иногда называют внутренней). Поэтому путать термины ПЗУ и ОЗУ либо RAM и ROM нельзя, они обозначают совершенно разные типы памяти и выполняют разные задачи. ОЗУ и RAM – это оперативная память, а ПЗУ и ROM – это постоянная (внутренняя) память.

Для чего нужна ОЗУ

Оперативная память или ОЗУ – это быстрая энергозависимая память, которая присутствует в любой компьютерной технике. Есть она и в мобильных устройствах, например, в телефонах, смартфонах и умных часах. ОЗУ используется для хранения данных, которые нужны процессору для работы. В частности, в оперативной памяти хранится код запущенных приложений и нужные им данные.

Как уже было сказано, основными особенностями ОЗУ являются высокая скорость работы и зависимость от питания. По факту оперативная память – это самая быстрая память в компьютере, если не считать регистры и кэш, которые находятся непосредственно в самом процессоре. Зависимость от питания означает, что оперативная память может хранить данные только пока присутствует напряжение электропитания. Как только напряжение пропадает, все данные в оперативной памяти обнуляются. Поэтому оперативная память используется только для временного хранения данных, которые нужны компьютеру для работы в данный момент. Для долговременного хранения данных используется постоянная память (ПЗУ, ROM), которая не зависит от питания и продолжает хранить информацию даже после полного выключения.

На что влияет объем ОЗУ

Производители телефонов, смартфонов и другой умной техники часто делают акцент на объеме ОЗУ. В рекламных материалах часто можно увидеть громкие заголовки, сообщающие о том, что устройство оснащено 2, 4, 6 или даже 8 гигабайтами оперативной памяти. Но, при этом производители редко объясняют, что конкретно получит пользователь если выберет устройство с таким объемом ОЗУ.

Большинство пользователей считают, что объем ОЗУ влияет на скорость работы их телефона. Частично так и есть, ведь чем больше объем оперативной памяти, тем реже системе нужно обращаться к постоянной памяти, которая заметно медленней. На практике, это означает, что телефон быстрее реагирует на действия пользователя, быстрее открывает приложения, реже перезагружает вкладки в браузере и т.д.

Но, нужно понимать, что скорость работы телефона также зависит от тактовой частоты процессора, количества вычислительных ядер, тактовой частоты оперативной памяти и программного обеспечения. Поэтому увеличение объема ОЗУ далеко не всегда дает улучшение, которое можно было бы заметить невооруженным взглядом.

Как посмотреть объем ОЗУ

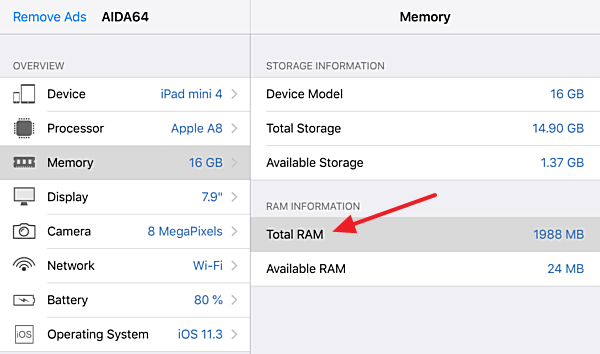

Если вы хотите узнать, какой объем ОЗУ установлен в вашем телефоне или смартфоне, то для этого можно воспользоваться специальными приложениями, предоставляющими информацию об устройстве. Например, можно воспользоваться приложением AIDA64, которое доступно как на Android, так и на iOS.

Если у вас телефон на базе Android, то вам нужно запустить приложение AIDA64 и перейти в раздел «Система».

А в случае iOS нужно запустить приложение AIDA64 и открыть раздел «Memory».

Также вы можете просто ввести название вашего устройства в любую поисковую систему и посмотреть характеристики в интернете.

Современная оперативная память (RAM FAQ 1.01)

SDRAM: Определение

Аббревиатура SDRAM расшифровывается как Synchronous Dynamic Random Access Memory синхронная динамическая память с произвольным доступом. Остановимся подробнее на каждом из этих определений. Под «синхронностью» обычно понимается строгая привязка управляющих сигналов и временных диаграмм функционирования памяти к частоте системной шины. Вообще говоря, в настоящее время изначальный смысл понятия синхронности становится несколько условным. Во-первых, частота шины памяти может отличаться от частоты системной шины (в качестве примера можно привести уже сравнительно давно существующий «асинхронный» режим работы памяти DDR SDRAM на платформах AMD K7 с чипсетами VIA KT333/400, в которых частоты системной шины процессора и шины памяти могут соотноситься как 133/166 или 166/200 МГц). Во-вторых, ныне существуют системы, в которых само понятие «системной шины» становится условным речь идет о платформах класса AMD Athlon 64 с интегрированным в процессор контроллером памяти. Частота «системной шины» (под которой в данном случае понимается не шина HyperTransport для обмена данными с периферией, а непосредственно «шина» тактового генератора) в этих платформах является лишь опорной частотой, которую процессор умножает на заданный коэффициент для получения собственной частоты. При этом контроллер памяти всегда функционирует на той же частоте, что и сам процессор, а частота шины памяти задается целым делителем, который может не совпадать с первоначальным коэффициентом умножения частоты «системной шины». Так, например, режиму DDR-333 на процессоре AMD Athlon 64 3200+ будут соответствовать множитель частоты «системной шины» 10 (частота процессора и контроллера памяти 2000 МГц) и делитель частоты памяти 12 (частота шины памяти 166.7 МГц). Таким образом, под «синхронной» операцией SDRAM в настоящее время следует понимать строгую привязку временных интервалов отправки команд и данных по соответствующим интерфейсам устройства памяти к частоте шины памяти (проще говоря, все операции в ОЗУ совершаются строго по фронту/срезу синхросигнала интерфейса памяти). Так, отправка команд и чтение/запись данных может осуществляться на каждом такте шины памяти (по положительному перепаду «фронту» синхросигнала; в случае памяти DDR/DDR2 передача данных происходит как по «фронту», так и по отрицательному перепаду «срезу» синхросигнала), но не по произвольным временным интервалам (как это осуществлялось в асинхронной DRAM).

Понятие «динамической» памяти, DRAM, относится ко всем типам оперативной памяти, начиная с самой древней, «обычной» асинхронной динамической памяти и заканчивая современной DDR2. Этот термин вводится в противоположность понятия «статической» памяти (SRAM) и означает, что содержимое каждой ячейки памяти периодически необходимо обновлять (ввиду особенности ее конструкции, продиктованной экономическими соображениями). В то же время, статическая память, характеризующаяся более сложной и более дорогой конструкцией ячейки и применяемая в качестве кэш-памяти в процессорах (а ранее и на материнских платах), свободна от циклов регенерации, т.к. в ее основе лежит не емкость (динамическая составляющая), а триггер (статическая составляющая).

Наконец, стоит также упомянуть о «памяти с произвольным доступом» Random Access Memory, RAM. Традиционно, это понятие противопоставляется устройствам «памяти только на чтение» Read-Only Memory, ROM. Тем не менее, противопоставление это не совсем верно, т.к. из него можно сделать вывод, что память типа ROM не является памятью с произвольным доступом. Это неверно, потому как доступ к устройствам ROM может осуществляться в произвольном, а не строго последовательном порядке. И на самом деле, наименование «RAM» изначально противопоставлялось ранним типам памяти, в которых операции чтения/записи могли осуществляться только в последовательном порядке. В связи с этим, более правильно назначение и принцип работы оперативной памяти отражает аббревиатура «RWM» (Read-Write Memory), которая, тем не менее, встречается намного реже. Заметим, что русскоязычным сокращениям RAM и ROM ОЗУ (оперативное запоминающее устройство) и ПЗУ (постоянное запоминающее устройство), соответственно, подобная путаница не присуща.

Микросхемы SDRAM: Физическая организация и принцип работы

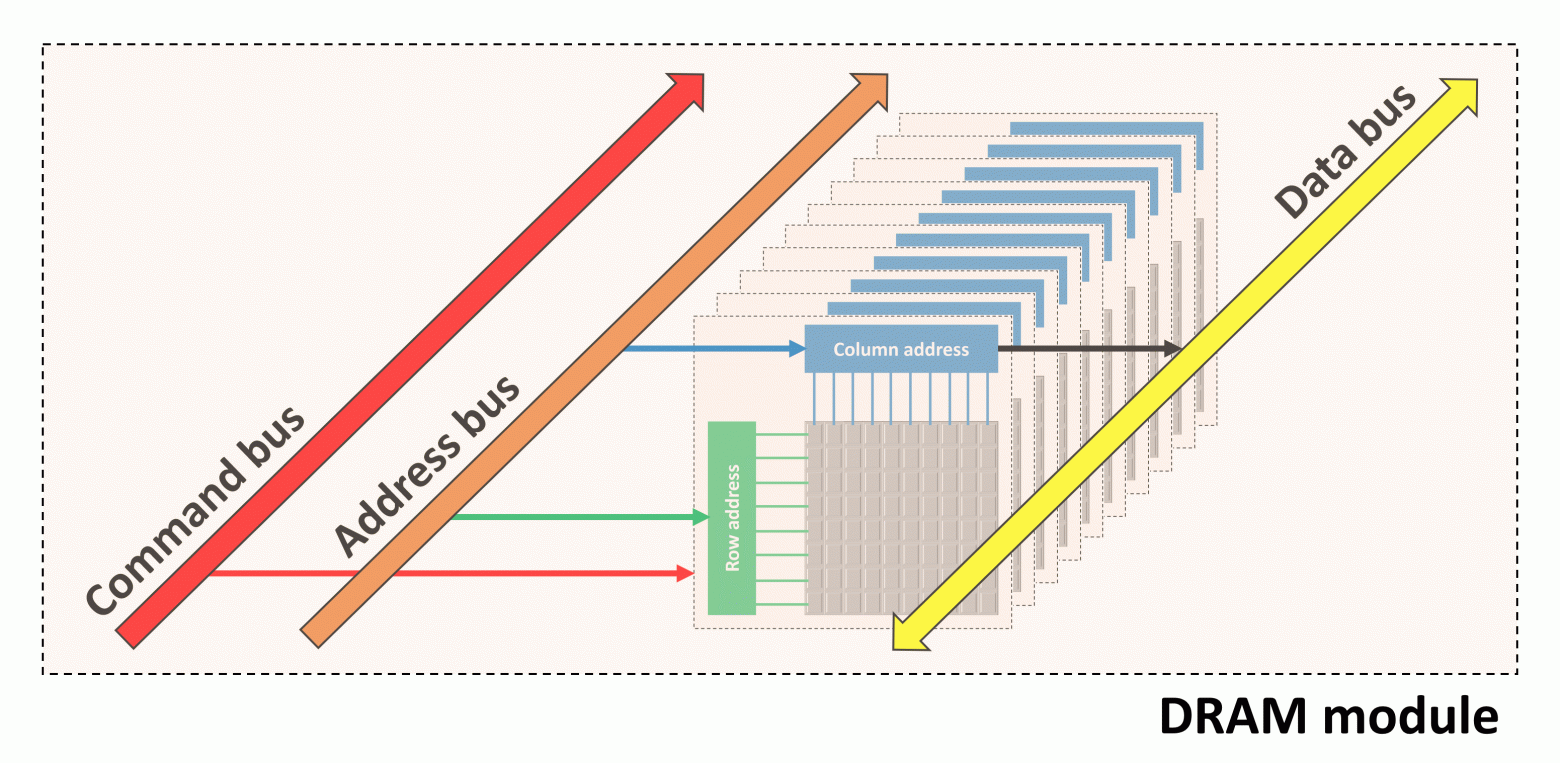

Общий принцип организации и функционирования микросхем динамической памяти (DRAM) практически един для всех ее типов как первоначальной асинхронной, так и современной синхронной. Исключение составляют разве что экзотические варианты, тем не менее, существовавшие еще до появления SDRAM, вроде Direct Rambus DRAM (DRDRAM). Массив памяти DRAM можно рассматривать как матрицу (двумерный массив) элементов (строго говоря, это понятие относится к логическому уровню организации микросхемы памяти, рассмотренному в следующем разделе, но его необходимо ввести здесь для наглядности), каждый из которых содержит одну или несколько физических ячеек (в зависимости от конфигурации микросхемы), способных вмещать элементарную единицу информации один бит данных. Ячейки представляют собой сочетание транзистора (ключа) и конденсатора (запоминающего элемента). Доступ к элементам матрицы осуществляется с помощью декодеров адреса строки и адреса столбца, которые управляются сигналами RAS# (сигнал выбора строки Row Access Strobe) и CAS# (сигнал выбора столбца Column Access Strobe).

Из соображений минимизации размера упаковки микросхемы, адреса строк и столбцов передаются по одним и тем же адресным линиям микросхемы иными словами, говорят о мультиплексировании адресов строк и столбцов (упомянутые выше отличия в общих принципах функционирования микросхем DRDRAM от «обычных» синхронных/асинхронных DRAM проявляются, в частности, здесь в этом типе микросхем памяти адреса строк и столбцов передаются по разным физическим интерфейсам). Так, например, 22-разрядный полный адрес ячейки может разделяться на два 11-разрядных адреса (строки и столбца), которые последовательно (через определенный интервал времени, см. раздел «Тайминги памяти») подаются на адресные линии микросхемы памяти. Одновременно со второй частью адреса (адреса столбца) по единому командно-адресному интерфейсу микросхемы SDRAM подается соответствующая команда (чтения или записи данных). Внутри микросхемы памяти адреса строки и столбца временно сохраняются в буферах (защелках) адреса строки и адреса столбца, соответственно.

Важно заметить, что с динамической матрицей памяти связан особый буфер статической природы, именуемый «усилителем уровня» (SenseAmp), размер которого равен размеру одной строки, необходимый для осуществления операций чтения и регенерации данных, содержащихся в ячейках памяти. Поскольку последние физически представляют собой конденсаторы, разряжающиеся при совершении каждой операции чтения, усилитель уровня обязан восстановить данные, хранящиеся в ячейке, после завершения цикла доступа (более подробно участие усилителя уровня в цикле чтения данных из микросхемы памяти рассмотрено ниже).

Кроме того, поскольку конденсаторы со временем теряют свой заряд (независимо от операций чтения), для предотвращения потери данных необходимо периодически обновлять содержимое ячеек. В современных типах памяти, которые поддерживают режимы автоматической регенерации (в «пробужденном» состоянии) и саморегенерации (в «спящем» состоянии), обычно это является задачей внутреннего контроллера регенерации, расположенного непосредственно в микросхеме памяти.

Схема обращения к ячейке памяти в самом общем случае может быть представлена следующим образом:

1. На адресные линии микросхемы памяти подается адрес строки. Наряду с этим подается сигнал RAS#, который помещает адрес в буфер (защелку) адреса строки.

2. После стабилизации сигнала RAS#, декодер адреса строки выбирает нужную строку, и ее содержимое перемещается в усилитель уровня (при этом логическое состояние строки массива инвертируется).

3. На адресные линии микросхемы памяти подается адрес столбца вместе с подачей сигнала CAS#, помещающего адрес в буфер (защелку) адреса столбца.

4. Поскольку сигнал CAS# также служит сигналом вывода данных, по мере его стабилизации усилитель уровня отправляет выбранные (соответствующие адресу столбца) данные в буфер вывода.

5. Сигналы CAS# и RAS# последовательно дезактивируются, что позволяет возобновить цикл доступа (по прошествии промежутка времени, в течение которого данные из усилителя уровня возвращаются обратно в массив ячеек строки, восстанавливая его прежнее логическое состояние).

Так выглядела реальная схема доступа к ячейке DRAM в самом первоначальном ее варианте, реализованном еще до появления первых реально используемых микросхем/модулей асинхронной памяти типа FPM (Fast Page Mode) DRAM. Тем не менее, нетрудно заметить, что эта схема является достаточно неоптимальной. Действительно, если нам требуется считать содержимое не одной, а сразу нескольких подряд расположенных ячеек, отличающихся только адресом столбца, но не адресом строки, то нет необходимости каждый раз подавать сигнал RAS# с одним и тем же адресом строки (т.е. выполнять шаги 1-2). Вместо этого, достаточно удерживать сигнал RAS# активным на протяжении промежутка времени, соответствующего, например, четырем последовательным циклам чтения (шаги 3-4, с последующей дезактивацией CAS#), после чего дезактивировать сигнал RAS#. Именно такая схема применялась в асинхронной памяти типа FPM DRAM и более поздней EDO (Enhanced Data Output) DRAM. Последняя отличалась опережающей подачей адреса следующего столбца, что позволяло достичь меньших задержек при операциях чтения.

В современных микросхемах SDRAM схема обращения к ячейкам памяти выглядит аналогично. Далее, в связи с обсуждением задержек при доступе в память (таймингов памяти), мы рассмотрим ее более подробно.

Микросхемы SDRAM: Логическая организация

А пока перейдем к рассмотрению организации микросхем памяти SDRAM на логическом уровне. Как уже было сказано выше, микросхема DRAM, фактически, представляет собой двумерный массив (матрицу) элементов, состоящих из одного или нескольких элементарных физических ячеек. Очевидно, что главной характеристикой этого массива является его емкость, выражаемая в количестве бит информации, которую он способен вместить. Часто можно встретить понятия «256-Мбит», «512-Мбит» микросхем памяти речь здесь идет именно об этом параметре. Однако составить эту емкость можно разными способами мы говорим сейчас не о количестве строк и столбцов, но о размерности, или «вместимости» индивидуального элемента. Последняя прямо связана с количеством линий данных, т.е. шириной внешней шины данных микросхемы памяти (но не обязательно с коэффициентом пропорциональности в единицу, что мы увидим ниже, при рассмотрении отличий памяти типа DDR и DDR2 SDRAM от «обычной» SDRAM). Ширина шины данных самых первых микросхем памяти составляла всего 1 бит, в настоящее же время наиболее часто встречаются 4-, 8- и 16- (реже 32-) битные микросхемы памяти. Таким образом, микросхему памяти емкостью 512 Мбит можно составить, например, из 128М (134 217 728) 4-битных элементов, 64М (67 108 864) 8-битных элементов или 32М (33 554 432) 16-битных элементов соответствующие конфигурации записываются как «128Mx4», «64Mx8» и «32Mx16». Первая из этих цифр именуется глубиной микросхемы памяти (безразмерная величина), вторая шириной (выраженная в битах).

Существенная отличительная особенность микросхем SDRAM от микросхем более ранних типов DRAM заключается в разбиении массива данных на несколько логических банков (как минимум 2, обычно 4). Не следует путать это понятие с понятием «физического банка» (называемого также «ранком» (rank) памяти), определенным для модуля, но не микросхемы памяти его мы рассмотрим далее. Сейчас лишь отметим, что внешняя шина данных каждого логического банка (в отличие от физического, который составляется из нескольких микросхем памяти для «заполнения» шины данных контроллера памяти) характеризуется той же разрядностью (шириной), что и разрядность (ширина) внешней шины данных микросхемы памяти в целом (x4, x8 или x16). Иными словами, логическое разделение массива микросхемы на банки осуществляется на уровне количества элементов в массиве, но не разрядности элементов. Таким образом, рассмотренные выше реальные примеры логической организации 512-Мбит микросхемы при ее «разбиении» на 4 банка могут быть записаны как 32Mx4x4 банка, 16Mx8x4 банка и 8Mx16x4 банка, соответственно. Тем не менее, намного чаще на маркировке микросхем памяти (либо ее расшифровке в технической документации) встречаются именно конфигурации «полной» емкости, без учета ее разделения на отдельные логические банки, тогда как подробное описание организации микросхемы (количество банков, строк и столбцов, ширину внешней шины данных банка) можно встретить лишь в подробной технической документации на данный вид микросхем SDRAM.

Разбиение массива памяти SDRAM на банки было введено, главным образом, из соображений производительности (точнее, минимизации системных задержек т.е. задержек поступления данных в систему). В самом простом и пока достаточном изложении, можно сказать, что после осуществления любой операции со строкой памяти, после дезактивации сигнала RAS#, требуется определенное время для осуществления ее «подзарядки». И преимущество «многобанковых» микросхем SDRAM заключается в том, что можно обращаться к строке одного банка, пока строка другого банка находится на «подзарядке». Можно расположить данные в памяти и организовать к ним доступ таким образом, что далее будут запрашиваться данные из второго банка, уже «подзаряженного» и готового к работе. В этот момент вполне естественно «подзаряжать» первый банк, и так далее. Такая схема доступа к памяти называется «доступом с чередованием банков» (Bank Interleave).

Модули SDRAM: Организация

Основные параметры логической организации микросхем памяти емкость, глубину и ширину, можно распространить и на модули памяти типа SDRAM. Понятие емкости (или объема) модуля очевидно это максимальный объем информации, который данный модуль способен в себя вместить. Теоретически он может выражаться и в битах, однако общепринятой «потребительской» характеристикой модуля памяти является его объем (емкость), выраженный в байтах точнее, учитывая современный уровень используемых объемов памяти в мега-, или даже гигабайтах.

Ширина модуля это разрядность его интерфейса шины данных, которая соответствует разрядности шины данных контроллера памяти и для всех современных типов контроллеров памяти SDRAM (SDR, DDR и DDR2) составляет 64 бита. Таким образом, все современные модули характеризуются шириной интерфейса шины данных «x64». Каким же образом достигается соответствие между 64-битная шириной шины данных контроллера памяти (64-битным интерфейсом модуля памяти), когда типичная ширина внешней шины данных микросхем памяти обычно составляет всего 4, 8 или 16 бит? Ответ очень прост интерфейс шины данных модуля составляется простым последовательным «слиянием» внешних шин данных индивидуальных микросхем модуля памяти. Такое «заполнение» шины данных контроллера памяти принято называть составлением физического банка памяти. Таким образом, для составления одного физического банка 64-разрядного модуля памяти SDRAM необходимо и достаточно наличие 16 микросхем x4, 8 микросхем x8 (это наиболее часто встречаемый вариант) или 4 микросхем x16.

Оставшийся параметр глубина модуля, являющийся характеристикой емкости (вместимости) модуля памяти, выраженной в количестве «слов» определенной ширины, вычисляется, как нетрудно догадаться, простым делением полного объема модуля (выраженного в битах) на его ширину (разрядность внешней шины данных, также выраженную в битах). Так, типичный 512-МБ модуль памяти SDR/DDR/DDR2 SDRAM имеет глубину, равную 512МБайт * 8 (бит/байт) / 64 бита = 64М. Соответственно, произведение ширины на глубину дает полную емкость модуля и определяет его организацию, или геометрию, которая в данном примере записывается в виде «64Мx64».

Возвращаясь к физическим банкам модуля памяти, заметим, что при использовании достаточно «широких» микросхем x8 или x16 ничего не мешает поместить и большее их количество, соответствующее не одному, а двум физическим банкам 16 микросхем x8 или 8 микросхем x16. Так различают однобанковые (или «одноранковые», single-rank) и двухбанковые («двухранковые», dual-rank) модули. Двухбанковые модули памяти наиболее часто представлены конфигурацией «16 микросхем x8», при этом один из физических банков (первые 8 микросхем) расположен с лицевой стороны модуля, а второй из них (оставшиеся 8 микросхем) с тыльной. Наличие более одного физического банка в модуле памяти нельзя считать определенным преимуществом, т.к. может потребовать увеличения задержек командного интерфейса, которые рассмотрены в соответствующем разделе.

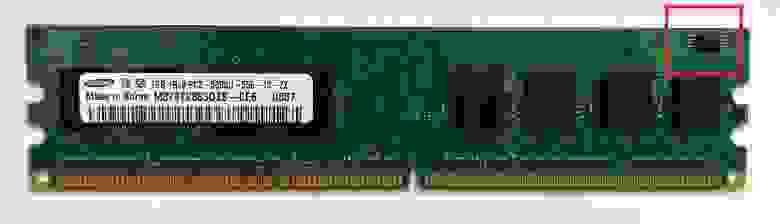

Модули памяти: Микросхема SPD

Еще до появления первого типа синхронной динамической оперативной памяти SDR SDRAM стандартом JEDEC предусматривается, что на каждом модуле памяти должна присутствовать небольшая специализированная микросхема ПЗУ, именуемая микросхемой «последовательного обнаружения присутствия» (Serial Presence Detect, SPD). Эта микросхема содержит основную информацию о типе и конфигурации модуля, временных задержках (таймингах, см. следующий раздел), которых необходимо придерживаться при выполнении той или иной операции на уровне микросхем памяти, а также прочую информацию, включающую в себя код производителя модуля, его серийный номер, дату изготовления и т.п. Последняя ревизия стандарта SPD модулей памяти DDR2 также включает в себя данные о температурном режиме функционирования модулей, которая может использоваться, например, для поддержания оптимального температурного режима посредством управления синхронизацией (регулированием скважности импульсов синхросигнала) памяти (так называемый «троттлинг памяти», DRAM Throttle). Более подробную информацию о микросхеме SPD и о том, как выглядит ее содержимое можно получить в нашей статье «SPD схема последовательного детектирования», а также в серии наших исследований модулей оперативной памяти.

Тайминги памяти

Немаловажной категорией характеристик микросхем/модулей памяти являются «тайминги памяти» понятие, наверняка так или иначе знакомое каждому пользователю ПК. Понятие «таймингов» тесно связано с задержками, возникающими при любых операциях с содержимым ячеек памяти в связи со вполне конечной скоростью функционирования устройств SDRAM, как и любых других интегральных схем. Задержки, возникающие при доступе в память, также принято называть «латентностью» памяти (этот термин не совсем корректен, и пришел в обиход с буквальным переводом термина latency, означающего «задержка»).

В этом разделе мы рассмотрим, где именно возникают задержки при операциях с данными содержимым микросхем памяти, и как они связаны с важнейшими параметрами таймингов памяти. Поскольку в настоящем руководстве мы рассматриваем модули памяти класса SDRAM (SDR, DDR и DDR2), ниже мы рассмотрим конкретную схему доступа к данным, содержащимся в ячейках памяти микросхемы SDRAM. В этом разделе мы также рассмотрим несколько иную категорию таймингов, связанных не с доступом к данным, но с выбором номера физического банка для маршрутизации команд по командному интерфейсу модулей памяти класса SDRAM так называемые «задержки командного интерфейса».

Схема доступа к данным микросхемы SDRAM

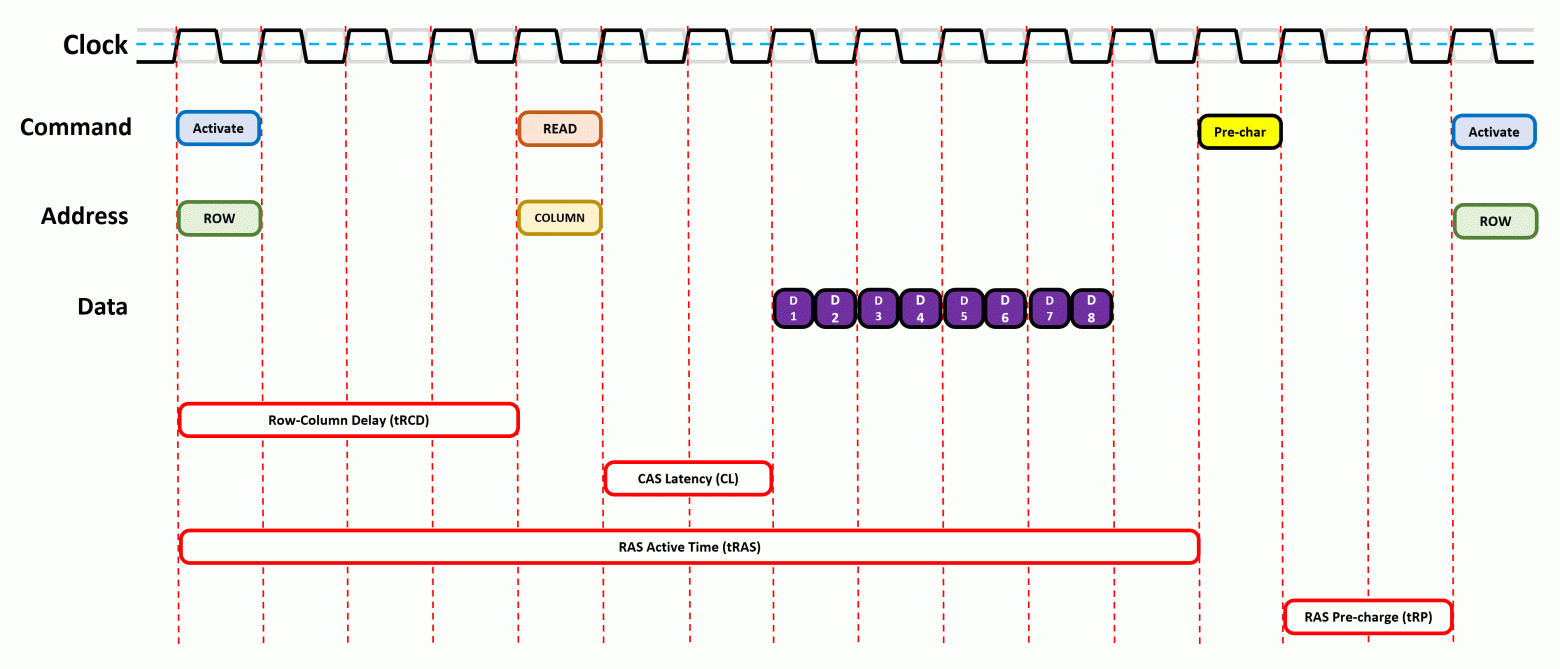

1. Активизация строки

Перед осуществлением любой операции с данными, содержащимися в определенном банке микросхемы SDRAM (чтения команда READ, или записи команда WRITE), необходимо «активизировать» соответствующую строку в соответствующем банке. С этой целью, на микросхему подается команда активизации (ACTIVATE) вместе с номером банка (линии BA0-BA1 для 4-банковой микросхемы) и адресом строки (адресные линии A0-A12, реальное количество которых зависит от количества строк в банке, в рассматриваемом примере 512-Мбит микросхемы памяти SDRAM их число составляет 2 13 = 8192).

Активизированная строка остается открытой (доступной) для последующих операций доступа до поступления команды подзарядки банка (PRECHARGE), по сути, закрывающей данную строку. Минимальный период «активности» строки от момента ее активации до момента поступления команды подзарядки, определяется минимальным временем активности строки (Row Active Time, tRAS).

Повторная активизация какой-либо другой строки того же банка не может быть осуществлена до тех пор, пока предыдущая строка этого банка остается открытой (т.к. усилитель уровня, содержащий буфер данных размером в одну строку банка и описанный в разделе «Микросхемы SDRAM: Физическая организация и принцип работы», является общим для всех строк данного банка микросхемы SDRAM). Таким образом, минимальный промежуток времени между активизацией двух различных строк одного и того же банка определяется минимальным временем цикла строки (Row Cycle Time, tRC).

В то же время, после активизации определенной строки определенного банка микросхеме SDRAM ничего не мешает активизировать какую-либо другую строку другого банка (в этом и заключается рассмотренное выше преимущество «многобанковой» структуры микросхем SDRAM) на следующем такте шины памяти. Тем не менее, в реальных условиях производителями устройств SDRAM обычно здесь также умышленно вводится дополнительная задержка, именуемая «задержкой от активации строки до активации строки» (Row-to-Row Delay, tRRD). Причины введения этой задержки не связаны с функционированием микросхем памяти как таковых и являются чисто электрическими операция активизации строки потребляет весьма значительное количество электрического тока, в связи с чем частое их осуществление может приводить к нежелательным избыточным нагрузкам устройства по току.

2. Чтение/запись данных

Следующий временной параметр функционирования устройств памяти возникает в связи с тем, что активизация строки памяти сама по себе требует определенного времени. В связи с этим, последующие (после ACTIVATE) команды чтения (READ) или записи (WRITE) данных не могут быть поданы на следующем такте шины памяти, а лишь спустя определенный временной интервал, называемый «задержкой между подачей адреса строки и столбца» (RAS#-to-CAS# Delay, tRCD).

Итак, после прошествия интервала времени, равного tRCD, при чтении данных в микросхему памяти подается команда READ вместе с номером банка (предварительно активизированного командой ACTIVATE) и адресом столбца. Устройства памяти типа SDRAM ориентированы на чтение и запись данных в пакетном (Burst) режиме. Это означает, что подача всего одной команды READ (WRITE) приведет к считыванию из ячеек (записыванию в ячейки) не одного, а сразу нескольких подряд расположенных элементов, или «слов» данных (разрядность каждого из которых равна ширине внешней шины данных микросхемы например, 8 бит). Количество элементов данных, считываемых одной командой READ или записываемых одной командой WRITE, называется «длиной пакета» (Burst Length) и обычно составляет 2, 4 или 8 элементов (за исключением экзотического случая передачи целой строки (страницы) «Full-Page Burst», когда необходимо дополнительно использовать специальную команду BURST TERMINATE для прерывания сверхдлинной пакетной передачи данных). Заметим, что для микросхем памяти типа DDR и DDR2 параметр Burst Length не может принимать значение меньше 2 и 4 элементов, соответственно причину этого мы рассмотрим ниже, в связи с обсуждением различий в реализации устройств памяти SDR/DDR/DDR2 SDRAM.

Возвращаясь к чтению данных, заметим, что существует две разновидности команды чтения. Первая из них является «обычным» чтением (READ), вторая называется «чтением с автоматической подзарядкой» (Read with Auto-Precharge, «RD+AP»). Последняя отличается тем, что после завершения пакетной передачи данных по шине данных микросхемы автоматически будет подана команда подзарядки строки (PRECHARGE), тогда как в первом случае выбранная строка микросхемы памяти останется «открытой» для осуществления дальнейших операций.

После подачи команды READ, первая порция данных оказывается доступной не сразу, а с задержкой в несколько тактов шины памяти, в течение которой данные, считанные из усилителя уровня, синхронизируются и передаются на внешние выводы микросхемы. Задержка между подачей команды чтения и фактическим «появлением» данных на шине считается наиболее важной и именуется пресловутой «задержкой сигнала CAS#» (CAS# Latency, tCL). Последующие порции данных (в соответствии с длиной передаваемого пакета) оказываются доступными без каких-либо дополнительных задержек, на каждом последующем такте шины памяти (по 1 элементу за такт для устройств SDR, по 2 элемента в случае устройств DDR/DDR2).

Операции записи данных осуществляются аналогичным образом. Точно также существуют две разновидности команд записи простая запись данных (WRITE) и запись с последующей автоматической подзарядкой строки (Write with Auto-Precharge, «WR+AP»). Точно также при подаче команды WRITE/WR+AP на микросхему памяти подаются номер банка и адрес столбца. Наконец, точно также запись данных осуществляется «пакетным» образом. Отличия операции записи от операции чтения следующие. Во-первых, первую порцию данных, подлежащих записи, необходимо подать по шине данных одновременно с подачей по адресной шине команды WRITE/WR+AP, номера банка и адреса столбца, а последующие порции, количество которых определяется длиной пакета на каждом последующем такте шины памяти. Во-вторых, вместо «задержки сигнала CAS#» (tCL) важной здесь является иная характеристика, именуемая «периодом восстановления после записи» (Write Recovery Time, tWR). Эта величина определяет минимальный промежуток времени между приемом последней порции данных, подлежащих записи, и готовности строки памяти к ее закрытию с помощью команды PRECHARGE. Если вместо закрытия строки требуется последующее считывание данных из той же самой открытой строки, то приобретает важность другая задержка, именуемая «задержкой между операциями записи и чтения» (Write-to-Read Delay, tWTR).

3. Подзарядка строки

Цикл чтения/записи данных в строки памяти, который в общем случае можно обозначить «циклом доступа к строке памяти», завершается закрытием открытой строки банка с помощью команды подзарядки строки PRECHARGE (которая, как мы уже отмечали выше, может быть «автоматической», т.е. являться составной частью команд «RD+AP» или «WR+AP»). Последующий доступ к этому банку микросхемы становится возможным не сразу, а по прошествию интервала времени, называемого «временем подзарядки строки» (Row Precharge Time, tRP). За этот период времени осуществляется собственно операция «подзарядки», т.е. возвращения элементов данных, соответствующих всем столбцам данной строки с усилителя уровня обратно в ячейки строки памяти.

Соотношения между таймингами

В заключение этой части, посвященной задержкам при доступе к данным, рассмотрим основные соотношения между важнейшими параметрами таймингов на примере более простых операций чтения данных. Как мы рассмотрели выше, в самом простейшем и самом общем случае — для пакетного считывания заданного количества данных (2, 4 или 8 элементов) необходимо осуществить следующие операции:

1) активизировать строку в банке памяти с помощью команды ACTIVATE;

2) подать команду чтения данных READ;

3) считать данные, поступающие на внешнюю шину данных микросхемы;

4) закрыть строку с помощью команды подзарядки строки PRECHARGE (как вариант, это делается автоматически, если на втором шаге использовать команду «RD+AP»).

Временной промежуток между первой и второй операцией составляет «задержку между RAS# и CAS#» (tRCD), между второй и третьей — «задержку CAS#» (tCL). Промежуток времени между третьей и четвертой операциями зависит от длины передаваемого пакета. Строго говоря, в тактах шины памяти он равен длине передаваемого пакета (2, 4 или 8), поделенного на количество элементов данных, передаваемых по внешней шине за один ее такт — 1 для устройств типа SDR, 2 для устройств типа DDR. Условно назовем эту величину «tBL».

Важно заметить, что микросхемы SDRAM позволяют осуществлять третью и четвертую операции в некотором смысле «параллельно». Чтобы быть точным команду подзарядки строки PRECHARGE можно подавать за некоторое количество тактов x до наступления того момента, на котором происходит выдача последнего элемента данных запрашиваемого пакета, не опасаясь при этом возникновения ситуации «обрыва» передаваемого пакета (последняя возникнет, если команду PRECHARGE подать после команды READ с временным промежутком, меньшим x). Не вдаваясь в подробности, отметим, что этот промежуток времени составляет величину, равную величине задержки сигнала CAS# за вычетом единицы (x = tCL — 1).

Наконец, промежуток времени между четвертой операцией и последующим повтором первой операции цикла составляет «время подзарядки строки» (tRP).

В то же время, минимальному времени активности строки (от подачи команды ACTIVATE до подачи команды PRECHARGE, tRAS), по его определению, как раз отвечает промежуток времени между началом первой и началом четвертой операции. Отсюда вытекает первое важное соотношение между таймингами памяти:

где tRCD время выполнения первой операции, tCL второй, (tBL — (tCL — 1)) третьей, наконец, вычитание единицы производится вследствие того, что период tRAS не включает в себя такт, на котором осуществляется подача команды PRECHARGE. Сокращая это выражение, получаем:

Достаточно поразительный вывод, вытекающий из детального рассмотрения схемы доступа к данным, содержащимся в памяти типа SDRAM, заключается в том, что минимальное значение tRAS не зависит(!) от величины задержки CAS#, tCL. Зависимость первого от последнего достаточно распространенное заблуждение, довольно часто встречающееся в различных руководствах по оперативной памяти.

В качестве примера первого соотношения, рассмотрим типичную высокоскоростную память типа DDR с величинами задержек (tCL-tRCD-tRP) 2-2-2. При минимальной длине пакета BL = 2 (минимально возможной для DDR) необходимо затратить не менее 1 такта шины памяти для передачи пакета данных. Таким образом, в этом случае минимальное значение tRAS оказывается равным 3 (столь малое значение tRAS не позволяет выставить подавляющее большинство контроллеров памяти). Передача более длинных пакетов, состоящих из 4 элементов (BL = 4, tBL = 2), увеличивает это значение до 4 тактов, наконец, для передачи максимального по длине 8-элементного пакета (BL = 8, tBL = 4) требуемое минимальное значение tRAS составляет 6 тактов. Отсюда следует, что, поскольку большинство контроллеров памяти не позволяют указать значение tRAS n n-prefetch» всегда соответствует минимальная величина Burst Length, равная 2 n (n = 1 соответствует DDR; n = 2 DDR2; n = 3 грядущей DDR3).

Что такое оперативная память смартфона (RAM) и сколько нужно Гб

Читайте, что такое оперативная память и сколько ее нужно смартфону, чтобы он справлялся с повседневными задачами. А сколько нужно RAM, чтобы играть в игры на высоких настройках. И нужно ли гнаться за 8 и 12Гб RAM.

Что такое оперативная память (RAM или ОЗУ)

Оперативная память (RAM, ОЗУ – аббревиатуры) – это кратковременное цифровое устройство хранения данных. Смартфоны, как и компьютеры, используют оперативную память в основном для хранения данных, которые используют запущенные приложения. Все потому, что оперативная память очень быстрая. Даже самый быстрый жесткий диск или флэш-накопитель работает медленно по сравнению с ОЗУ.

Сколько RAM бывает в смартфонах

Еще в первые годы появления Android в смартфонах было 512 МБ памяти, а флагманы могли похвастаться даже 1 ГБ. Так началась революция в мире телефонов и смартфонов. Со временем RAM становилось только больше. К 2018 году большинство высокотехнологичных смартфонов имели на борту 3 ГБ оперативной памяти, а в 2018 и 2019 годах 4 ГБ стали фактическим стандартом. Казалось бы, куда еще больше? Но в продаже все больше телефонов с 6 ГБ, 8 ГБ, даже 10 ГБ и 12 ГБ ОЗУ.

Наверняка у вас дома есть ноутбуки под управлением Windows 10 с 4 ГБ оперативной памяти. MacBook имеет 8 ГБ оперативной памяти и может работать с требовательными приложениями, такими как Premiere Pro или Photoshop. Неужели, вы всерьез думаете, что телефону требуется больше оперативной памяти, чем ноутбуку?

Как Android смартфон использует оперативную память

Чтобы понять, достаточно ли смартфону оперативной памяти и сколько ее должно быть, надо разобраться, как она используется.

Когда вы запускаете новое приложение на Android, ядро Linux создает новый процесс. Процесс – это единица исполнения с собственным виртуальным адресным пространством (которое сопоставляется с физической памятью). Ядро Linux управляет ресурсами, необходимыми для этого процесса. Сюда входят: время работы процессора, ввод и вывод данных и физическую память (RAM).

Когда имеется достаточно ресурсов, работа ядра проста. Если процесс требует больше процессорного времени, ядро может легко предоставить ему больше времени на выполнение и больше оперативной памяти.

Однако, когда ресурсы ограничены, все усложняется. Если процессор (CPU) смартфона перегружен, то ядро ждет завершения процесса. И все это время, выделенная оперативная память все еще занята. А если таких процессов много? Они быстро могут скушать всю вашу RAM. И телефон станет ни на что не реагирующим кирпичом.

Linux и Android справляются с этой проблемой двумя способами.

Первый способ, когда Android может выделить часть внутренней памяти (ROM) для файла подкачки. Именно так поступают ОС на компьютерах. При недостатке памяти на диск записываются самые старые и наименее используемые части оперативной памяти. И занимаемая ими RAM становится доступной для других процессов. Если позднее эти данные потребуются, они считываются с диска и записываются обратно в оперативную память.

Второй способ смартфону быть быстрым – “убивать” старые процессы. Обычно это те, что были запущены давно и на данный момент не используются

На самом деле, все телефоны обязательно используют первый и второй способы. Больший объем оперативной памяти позволяет реже использовать “убийство”. Именно поэтому компании-производители увеличивают объем оперативной памяти телефонов буквально каждый год.

Какой вывод можно сделать из этой информации? Производители смартфонов не виновны в постоянном росте оперативной памяти. В конце концов, разработчики мобильных приложений и игр делают их все более тяжелыми и требовательными.

Какой объем RAM используют приложения?

Приложения тоже бывают разные. Есть встроенные (стандартные), без которых работа смартфона не возможна. Например приложение “Телефон”. Есть игры и мультимедийные программы. Браузеры. У всех у них совершенно разные аппетиты.

Стандартные приложения используют от 130 Мб до 400 Мб оперативной памяти. Существуют такие приложения, как YouTube и WhatsApp, а еще казуальные игры, типа Crossy Road и Candy Crush. Также есть “медиа-приложения”, которые загружают большое количество изображений и поэтому используют больше RAM для их отображения. Например, Google Photos и Instagram. Эти приложения используют от 400 Мб до 700 Мб оперативной памяти.

Наконец, появились “огромные” приложения, преимущественно высококлассные 3D-игры. Эти монстры сжирают гигабайты RAM вашего смартфона, как голодный Pac-Man. Например, PUBG Mobile может использовать от 800 МБ до 1152 МБ ОЗУ.

Вы не поверите, но браузер Google Chrome также относится к категории монстров (всего с тремя открытыми вкладками).

Сколько оперативной памяти нужно смартфону?

Объем оперативной памяти, используемой на устройстве, полностью зависит от того, какие приложения у вас запущены. Если вам нравится Instagram и Candy Crush, но не больше, то вы будете использовать чуть больше 1 ГБ оперативной памяти. Если постоянно играете в PUBG и Asphalt 9, вам понадобится 2GB только на игры.

Не забывайте, что еще сама операционная система тоже требует от 500 до 1 ГБ оперативной памяти. Плюс фоновые процессы, которые постоянно висят в памяти. Например, Viber или другой мессенджер. Т.е. не весь объем оперативной памяти вам доступен.

Доступная оперативная память – это объем RAM, свободный для запуска новых приложений без “убийства” предыдущих.

Huawei Mate 8, Google Pixel 3 XL и Samsung Note 8 позволяют вам использовать всего около 50-60% установленной оперативной памяти. Остальную они резервируют на нужды операционной системы и своих фирменных прошивок и приложений.

Смартфоны типа Pixel 3 XL могут хранить в оперативной памяти не менее пяти “стандартных” приложений без удаления. Это означает, что вы можете переключаться между YouTube, WhatsApp, Spotify, Candy Crush и Google Play без проблем.

Если вы запустите больше приложений, Pixel 3 XL начнет более агрессивно использовать файл подкачки, пытаясь освободить память. Это означает, что на самом деле, вы можете запустить около восьми “стандартных” приложений и сохранить их все в памяти и файле подкачки. Переключение на приложение, которое было перенесено из оперативной памяти в подкачку, приведет к небольшой задержке.

Если вы запустите более восьми “стандартных” приложений, одно из предыдущих будет удалено из памяти. И будет запускаться в следующий раз с нуля.

Если приложение выгружается из RAM, это не обязательно плохо. Вы сами не раз с этим сталкивались. Такое приложение будет перезагружаться при включении.

Смартфоны с 6 ГБ оперативной памяти, такие как Samsung Note 8 и 9, отдают пользователю всего около 2,5- 3,5 ГБ RAM. Оба устройства также имеют как минимум файл подкачки в ROM размером 2 Гб. Это означает, что вы можете переключаться между тяжелой игрой (или Chrome), мультимедийным приложением (например, Instagram) и 5 или более стандартными приложениями, и все останется в оперативной памяти. Если вы запустите дополнительные приложения, телефон начнет использовать файл подкачки.

6Гб оперативной памяти в смартфоне – идеальный вариант!

Такой объем RAM означает зону комфорта для пользователя смартфона. Стандартные приложения остаются в памяти в течение длительного периода времени, а многозадачность быстрой. Вы не будете замечать переключения между приложениями и играми.

Телефоны с 6 ГБ оперативной памяти могут переключаться между десятками и более приложений, включая некоторые сверхмощные. И вы даже не заметите перезагрузки некоторых приложений.

Естественно, смартфоны с 8ГБ RAM в плане плавности работы еще лучше. Они могут хранить в памяти, по крайней мере, дюжину приложений без перезагрузки. Даже такие крупные, как PUBG и Google Photo. Переключение между приложениями происходит без проблем.

Зачем нужны смартфоны с 8ГБ и больше RAM?

В отличие от компьютеров, для смартфонов на Android, не делают приложения, которые они не смогут запустить! Даже с 3 ГБ оперативной памяти мы не говорим о том, какие приложения потянет смартфон. Мы всего лишь учитываем, сколько приложений он может одновременно хранить в памяти! Смартфоны с 4ГБ работают хорошо, с 6ГБ отлично, с 8Гб уже, наверно, и слишком. 10 ГБ, 12 ГБ, 16 ГБ – это просто глупость. Это примеры маркетинговых хитростей, которые увеличивает цену и не приносит пользы пользователю или приносит совершенно мало пользы.

RAM – что это, как работает, виды, особенности, характеристики

Вопросы по поводу термина RAM, что это, как работает, где и для чего используется, могут появиться у пользователя, заметившего такое название в описаниях характеристик ПК, требованиях к компьютерным программам и играм.

Аббревиатура образована от английского названия памяти с произвольным доступом (Random Access Memory) и на русском языке называется оперативным запоминающим устройством или ОЗУ.

В RAM хранятся обрабатываемые процессором данные и выполняемый код – но только пока работает вычислительное устройство.

Назначение и принцип работы

Основным назначением RAM является хранение временных данных, необходимых компьютеру только во время его работы.

В эту память загружаются данные, которые будут выполняться процессором напрямую.

Принцип работы RAM следующий:

Рис. 2. Общая схема обработки данных вычислительной техникой.

Важно: При подаче электрического сигнала на определённую строку открываются все её транзисторы. Отсюда следует, что минимальным объёмом данных, который считывается из памяти, является не ячейка, а строка.

Из-за того что принцип действия RAM основан на полупроводниках, хранящиеся в этой памяти данные остаются доступными только при подаче электротока.

При отключении напряжения питание обрывается, а все данные в ОЗУ полностью стираются.

Виды и особенности RAM

Существует два вида операционной памяти – статическая SRAM и динамическая DRAM.

Первая обычно имеет небольшой объём (в пределах нескольких мегабайт) и используется как кэш.

Её преимуществами являются повышенная надёжность и производительность, а недостатками – высокая стоимость и небольшая плотность размещений транзисторов.

Рис. 3. Память типа SRAM.

В качестве ОЗУ для вычислительной техники SRAM не применяется из-за того что размеры планок «оперативки» были бы слишком большими.

Для оперативной памяти больше подходит DRAM – скорость её работы ниже, однако эта версия RAM выигрывает за счёт небольшой цены и высокой плотности расположения полупроводников.

Рис. 4. Модули DRAM.

Конструктивные исполнения DRAM

В зависимости от выполняемых задач модули динамической памяти DRAM выпускаются в различном исполнении:

Рис. 5. Память SIPP.

Рис. 6. Отличия модулей DIMM и SO-DIMM.

Ещё один вариант DRAM – модули RIMM, которые из-за особенностей конструкции устанавливаются только парами, хотя сейчас практически не применяются. Память имеет 160, 168, 184 и 242 контакта. Существует уменьшенная разновидность этой «оперативки», SO-RIMM, предназначенная для портативных компьютеров.

Основные параметры RAM

Одной из главных характеристик RAM, на которые обращают внимание практически все пользователи ПК, является её объём.

В какой-то степени, это правильно, но при выборе оперативной памяти для компьютера стоит ориентироваться ещё и по таким рабочим параметрам:

Все эти параметры связаны. Так, ОЗУ типа DDR1 может иметь рабочую частоту шины от 200 до 400 МГц, DDR2 – от 200 до 533 МГц, DDR3 – 800 до 2400 МГц.

Аналогичный показатель более современных модулей DDR4 достигает уже 3200 МГц, что позволяет ей работать заметно быстрее.

Все параметры RAM должны соответствовать характеристикам материнской платы и центрального процессора компьютера. При этом память другого типа просто не получится установить из-за несовпадения контактов и слотов, ОЗУ с неподходящей частотой может работать некорректно, а неподдерживаемый объём не позволит компьютеру запуститься. Например, 8-гигабайтный модуль DIMM не стоит устанавливать на «материнку» с поддержкой только 4 Гб для каждого слота.

Тайминги и напряжение

Таймингом называется продолжительность задержки в процессе передачи информации между различными компонентами вычислительной техники.

Его значение непосредственно влияет на скорость работы RAM, а значит, и всего компьютера (или другого устройства).

Небольшой тайминг означает, что операции будут выполняться быстрее.

Время задержки обратно пропорционально быстродействию ОЗУ.

Для решения проблемы производители RAM повышают рабочее напряжение, уменьшая тайминги. Это позволяет увеличить число выполняемых за единицу времени операций, однако требует и более ответственного отношения к выбору памяти, которая должна совпадать ещё по вольтажу.

Объём ОЗУ

Один из главных параметров RAM, объём, должен не только совпадать с характеристиками материнской платы, но и соответствовать требованиям пользователя.

В настоящее время оптимальным вариантом для среднего ПК является показатель в 4–8 Гб.

Для офисных компьютеров может хватить и 1–2 Гб, но большинство современных программ будут зависать, для игровых моделей размер ОЗУ должен быть не меньше 8–16 Гб.

Частота и быстродействие RAM

Пропускная способность оперативной памяти зависит от её частоты – параметра, который тоже связан с возможностями материнской платы и ЦПУ.

При установке RAM со скоростью передачи данных 1600 миллионов операций в секунды (МГц) на устаревшем компьютере модуль будет работать медленнее.

Если материнская плата и процессор поддерживают, например, только 1066 МГц, такая же частота будет и у ОЗУ.

Рис. 7. Показатели RAM на планке памяти.

Выводы

Принцип действия и другие характеристики RAM стоит знать не только специалистам, которые занимаются сборкой вычислительной техники, но и обычным пользователям.

Тем более что никто не мешает любому владельцу компьютера самостоятельно подобрать подходящий модуль ОЗУ.

Но делать это без сравнения показателей памяти и других комплектующих ПК не рекомендуется.

Анатомия RAM

У каждого компьютера есть ОЗУ, встроенное в процессор или находящееся на отдельной подключенной к системе плате — вычислительные устройства просто не смогли бы работать без оперативной памяти. ОЗУ — потрясающий образец прецизионного проектирования, однако несмотря на тонкость процессов изготовления, память ежегодно производится в огромных объёмах. В ней миллиарды транзисторов, но она потребляет только считанные ватты мощности. Учитывая большую важность памяти, стоит написать толковый анализ её анатомии.

Итак, давайте приготовимся к вскрытию, выкатим носилки и отправимся в анатомический театр. Настало время изучить все подробности каждой ячейки, из которых состоит современная память, и узнать, как она работает.

Зачем же ты, RAM-ео?

Процессорам требуется очень быстро получать доступ к данным и командам, чтобы программы выполнялись мгновенно. Кроме того, им нужно, чтобы при произвольных или неожиданных запросах не очень страдала скорость. Именно поэтому для компьютера так важно ОЗУ (RAM, сокращение от random-access memory — память с произвольным доступом).

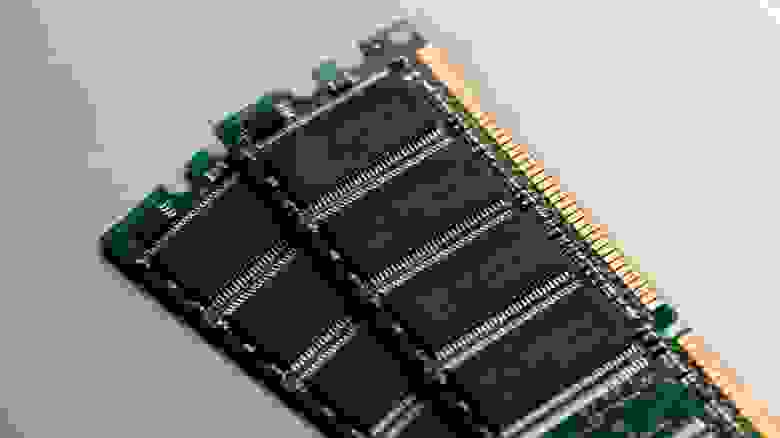

Существует два основных типа RAM: статическая и динамическая, или сокращённо SRAM и DRAM.

Мы будем рассматривать только DRAM, потому что SRAM используется только внутри процессоров, таких как CPU или GPU. Так где же находится DRAM в наших компьютерах и как она работает?

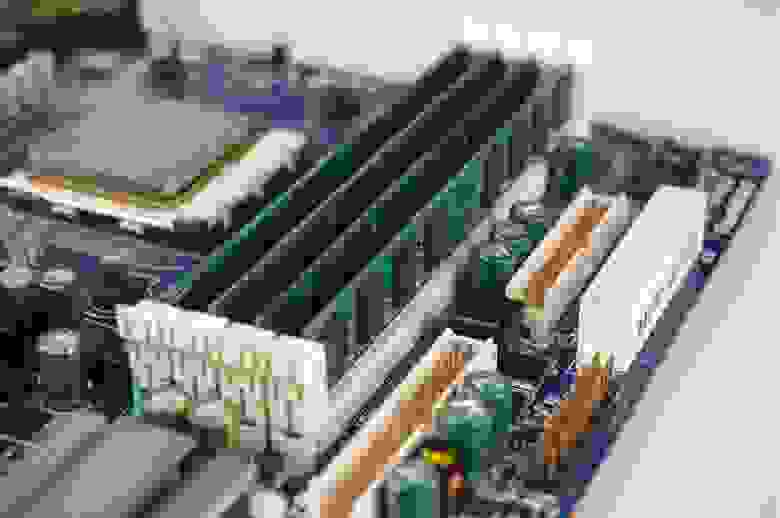

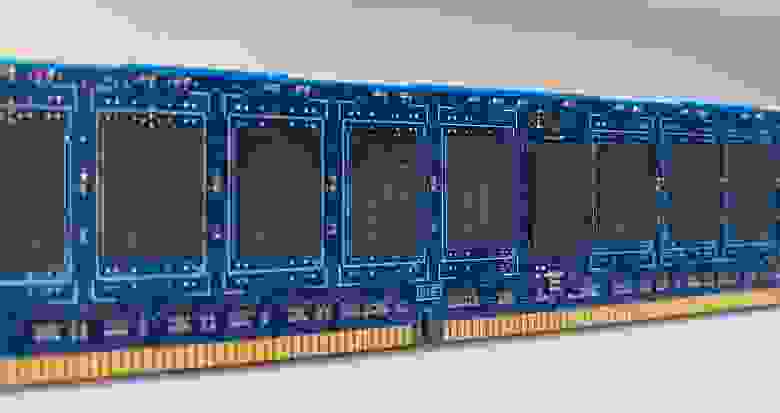

Большинству людей знакома RAM, потому что несколько её планок находится рядом с CPU (центральным процессором, ЦП). Эту группу DRAM часто называют системной памятью, но лучше её называть памятью CPU, потому что она является основным накопителем рабочих данных и команд процессора.

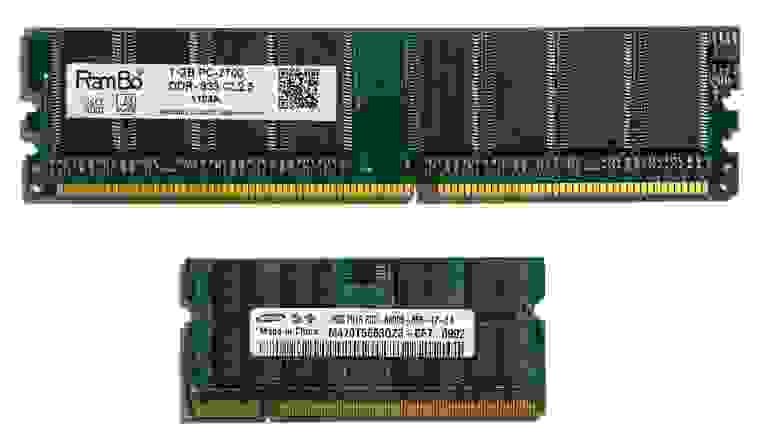

Как видно на представленном изображении, DRAM находится на небольших платах, вставляемых в материнскую (системную) плату. Каждую плату обычно называют DIMM или UDIMM, что расшифровывается как dual inline memory module (двухсторонний модуль памяти) (U обозначает unbuffered (без буферизации)). Подробнее мы объясним это позже; пока только скажем, что это самая известная RAM любого компьютера.

Она не обязательно должна быть сверхбыстрой, но современным ПК для работы с большими приложениями и для обработки сотен процессов, выполняемых в фоновом режиме, требуется много памяти.

Ещё одним местом, где можно найти набор чипов памяти, обычно является графическая карта. Ей требуется сверхбыстрая DRAM, потому что при 3D-рендеринге выполняется огромное количество операций чтения и записи данных. Этот тип DRAM предназначен для несколько иного использования по сравнению с типом, применяемым в системной памяти.

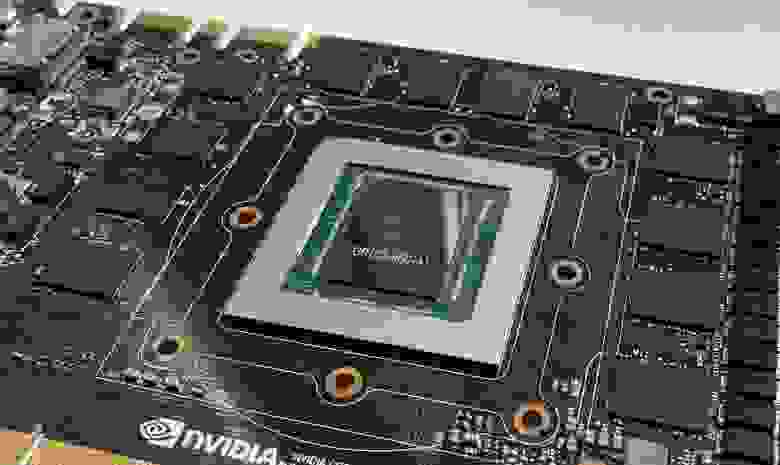

Ниже вы видите GPU, окружённый двенадцатью небольшими пластинами — это чипы DRAM. Конкретно этот тип памяти называется GDDR5X, о нём мы поговорим позже.

Графическим картам не нужно столько же памяти, как CPU, но их объём всё равно достигает тысяч мегабайт.

Не каждому устройству в компьютере нужно так много: например, жёстким дискам достаточно небольшого количества RAM, в среднем по 256 МБ; они используются для группировки данных перед записью на диск.

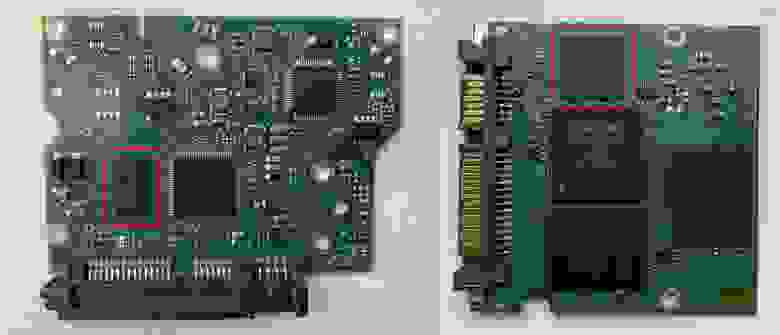

На этих фотографиях мы видим платы HDD (слева) и SSD (справа), на которых отмечены чипы DRAM. Заметили, что чип всего один? 256 МБ сегодня не такой уж большой объём, поэтому вполне достаточно одного куска кремния.

Узнав, что каждый компонент или периферийное устройство, выполняющее обработку, требует RAM, вы сможете найти память во внутренностях любого ПК. На контроллерах SATA и PCI Express установлены небольшие чипы DRAM; у сетевых интерфейсов и звуковых карт они тоже есть, как и у принтеров со сканнерами.

Если память можно встретить везде, она может показаться немного скучной, но стоит вам погрузиться в её внутреннюю работу, то вся скука исчезнет!

Скальпель. Зажим. Электронный микроскоп.

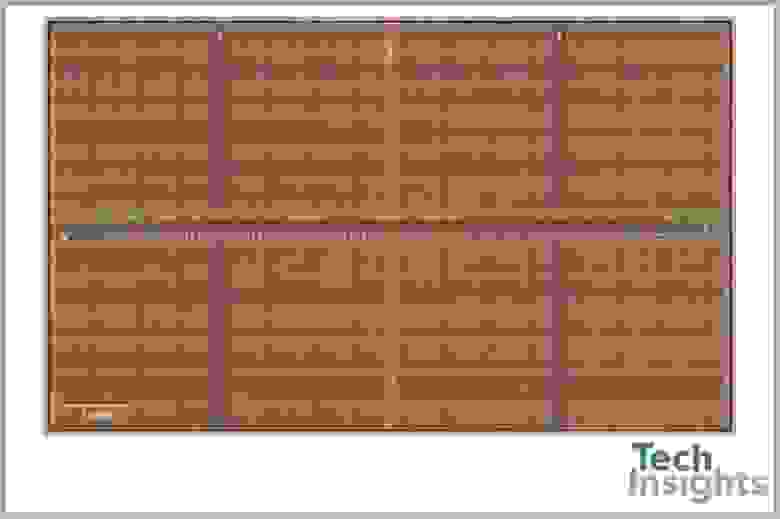

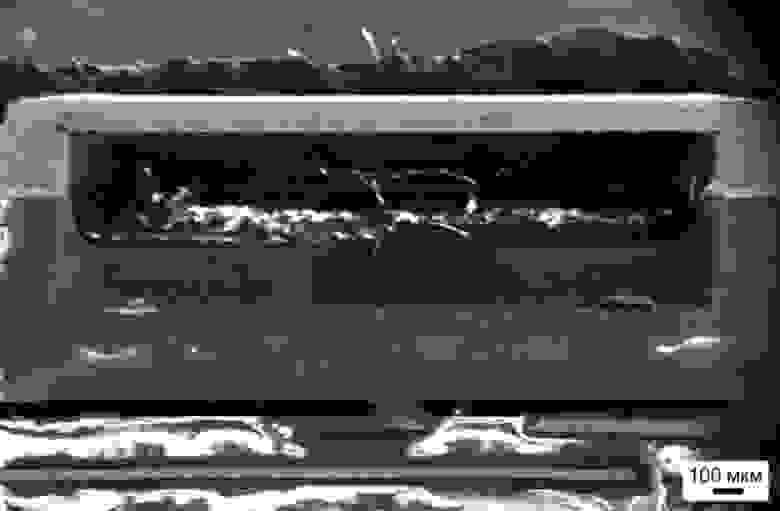

У нас нет всевозможных инструментов, которые инженеры-электронщики используют для изучения своих полупроводниковых творений, поэтому мы не можем просто разобрать чип DRAM и продемонстрировать вам его внутренности. Однако такое оборудование есть у ребят из TechInsights, которые сделали этот снимок поверхности чипа:

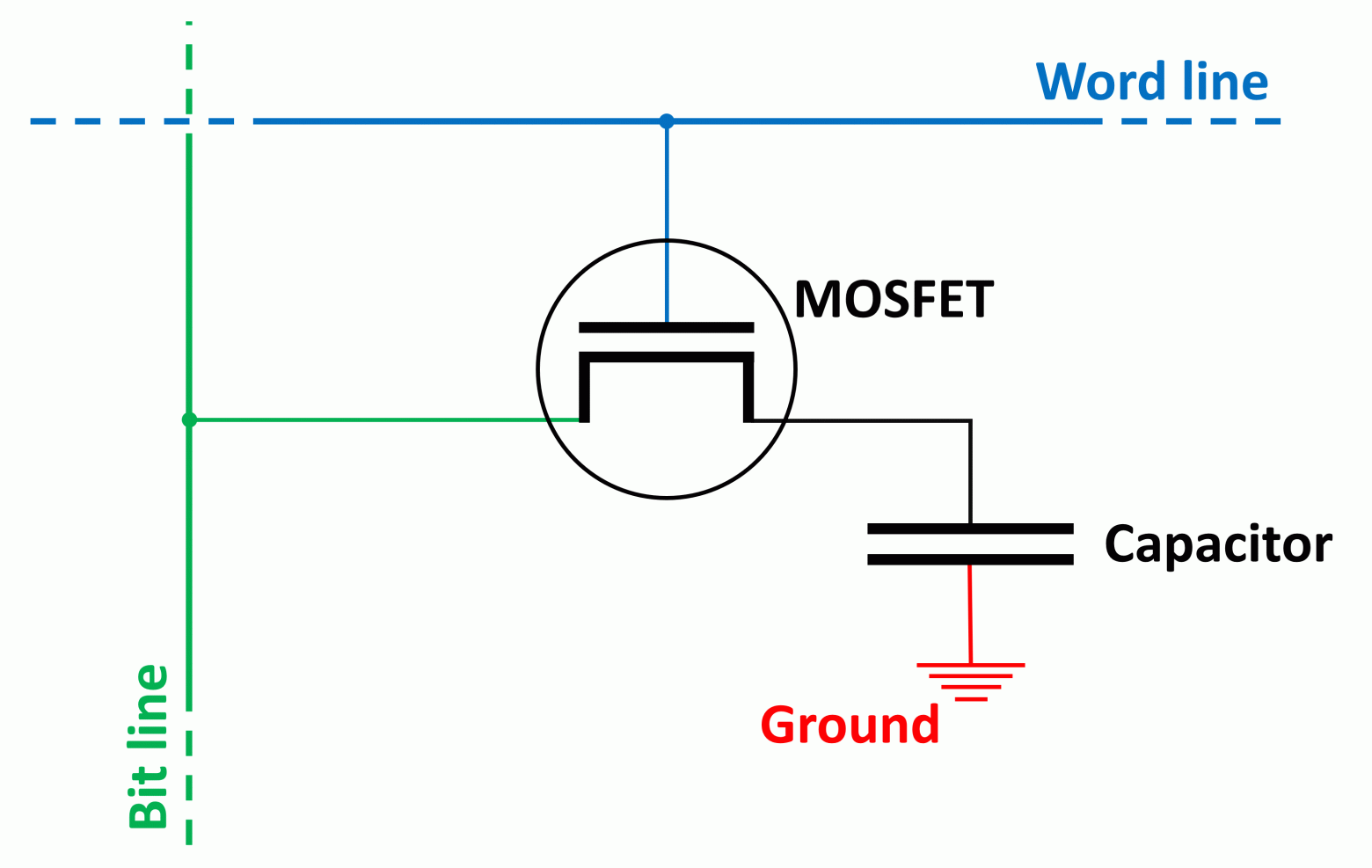

Если вы подумали, что это похоже на сельскохозяйственные поля, соединённые тропинками, то вы не так далеки от истины! Только вместо кукурузы или пшеницы поля DRAM в основном состоят из двух электронных компонентов:

Синими и зелёными линиями обозначены соединения, подающие напряжение на МОП-транзистор и конденсатор. Они используются для считывания и записи данных в ячейку, и первой всегда срабатывает вертикальная (разрядная) линия.

Канавочный конденсатор, по сути, используется в качестве сосуда для заполнения электрическим зарядом — его пустое/заполненное состояние даёт нам 1 бит данных: 0 — пустой, 1 — полный. Несмотря на предпринимаемые инженерами усилия, конденсаторы не способны хранить этот заряд вечно и со временем он утекает.

Это означает, что каждую ячейку памяти нужно постоянно обновлять по 15-30 раз в секунду, хотя сам этот процесс довольно быстр: для обновления набора ячеек требуется всего несколько наносекунд. К сожалению, в чипе DRAM множество ячеек, и во время их обновления считывание и запись в них невозможна.

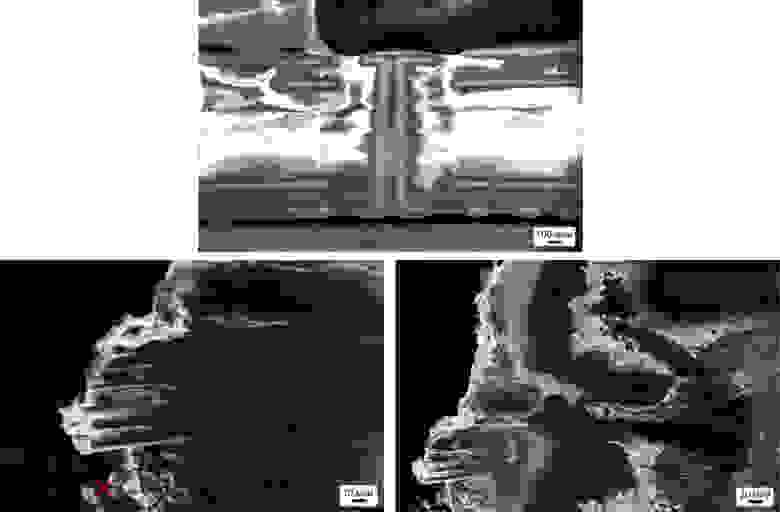

К каждой линии подключено несколько ячеек:

Строго говоря, эта схема неидеальна, потому что для каждого столбца ячеек используется две разрядные линии — если бы мы изобразили всё, то схема бы стала слишком неразборчивой.

Полная строка ячеек памяти называется страницей, а длина её зависит от типа и конфигурации DRAM. Чем длиннее страница, тем больше в ней бит, но и тем большая электрическая мощность нужна для её работы; короткие страницы потребляют меньше мощности, но и содержат меньший объём данных.

Однако нужно учитывать и ещё один важный фактор. При считывании и записи на чип DRAM первым этапом процесса является активация всей страницы. Строка битов (состоящая из нулей и единиц) хранится в буфере строки, который по сути является набором усилителей считывания и защёлок, а не дополнительной памятью. Затем активируется соответствующий столбец для извлечения данных из этого буфера.

Если страница слишком мала, то чтобы успеть за запросами данных, строки нужно активировать чаще; и наоборот — большая страница предоставляет больше данных, поэтому активировать её можно реже. И даже несмотря на то, что длинная строка требует большей мощности и потенциально может быть менее стабильной, лучше стремиться к получению максимально длинных страниц.

Если собрать вместе набор страниц, то мы получим один банк памяти DRAM. Как и в случае страниц, размер и расположение строк и столбцов ячеек играют важную роль в количестве хранимых данных, скорости работы памяти, энергопотреблении и так далее.

Например, схема может состоять из 4 096 строк и 4 096 столбцов, при этом полный объём одного банка будет равен 16 777 216 битам или 2 мегабайтам. Но не у всех чипов DRAM банки имеют квадратную структуру, потому что длинные страницы лучше, чем короткие. Например, схема из 16 384 строк и 1 024 столбцов даст нам те же 2 мегабайта памяти, но каждая страница будет содержать в четыре раза больше памяти, чем в квадратной схеме.

Все страницы в банке соединены с системой адресации строк (то же относится и к столбцам) и они контролируются сигналами управления и адресами для каждой строки/столбца. Чем больше строк и столбцов в банке, тем больше битов должно использоваться в адресе.

Для банка размером 4 096 x 4 096 для каждой системы адресации требуется 12 бит, а для банка 16 384 x 1 024 потребуется 14 бит на адреса строк и 10 бит на адреса столбцов. Стоит заметить, что обе системы имеют суммарный размер 24 бита.

Если бы чип DRAM мог предоставлять доступ к одной странице за раз, то это было бы не особо удобно, поэтому в них упаковано несколько банков ячеек памяти. В зависимости от общего размера, чип может иметь 4, 8 или даже 16 банков — чаще всего используется 8 банков.

Все эти банки имеют общие шины команд, адресов и данных, что упрощает структуру системы памяти. Пока один банк занят работой с одной командой, другие банки могут продолжать выполнение своих операций.

Весь чип, содержащий все банки и шины, упакован в защитную оболочку и припаян к плате. Она содержит электропроводники, подающие питание для работы DRAM и сигналов команд, адресов и данных.

На фотографии выше показан чип DRAM (иногда называемый модулем), изготовленный компанией Samsung. Другими ведущими производителями являются Toshiba, Micron, SK Hynix и Nanya. Samsung — крупнейший производитель, он имеет приблизительно 40% мирового рынка памяти.

Каждый изготовитель DRAM использует собственную систему кодирования характеристик памяти; на фотографии показан чип на 1 гигабит, содержащий 8 банков по 128 мегабита, выстроенных в 16 384 строки и 8 192 столбца.

Выше по рангу

Компании-изготовители памяти берут несколько чипов DRAM и устанавливают их на одну плату, называемую DIMM. Хотя D расшифровывается как dual (двойная), это не значит, что на ней два набора чипов. Под двойным подразумевается количество электрических контактов в нижней части платы; то есть для работы с модулями используются обе стороны платы.

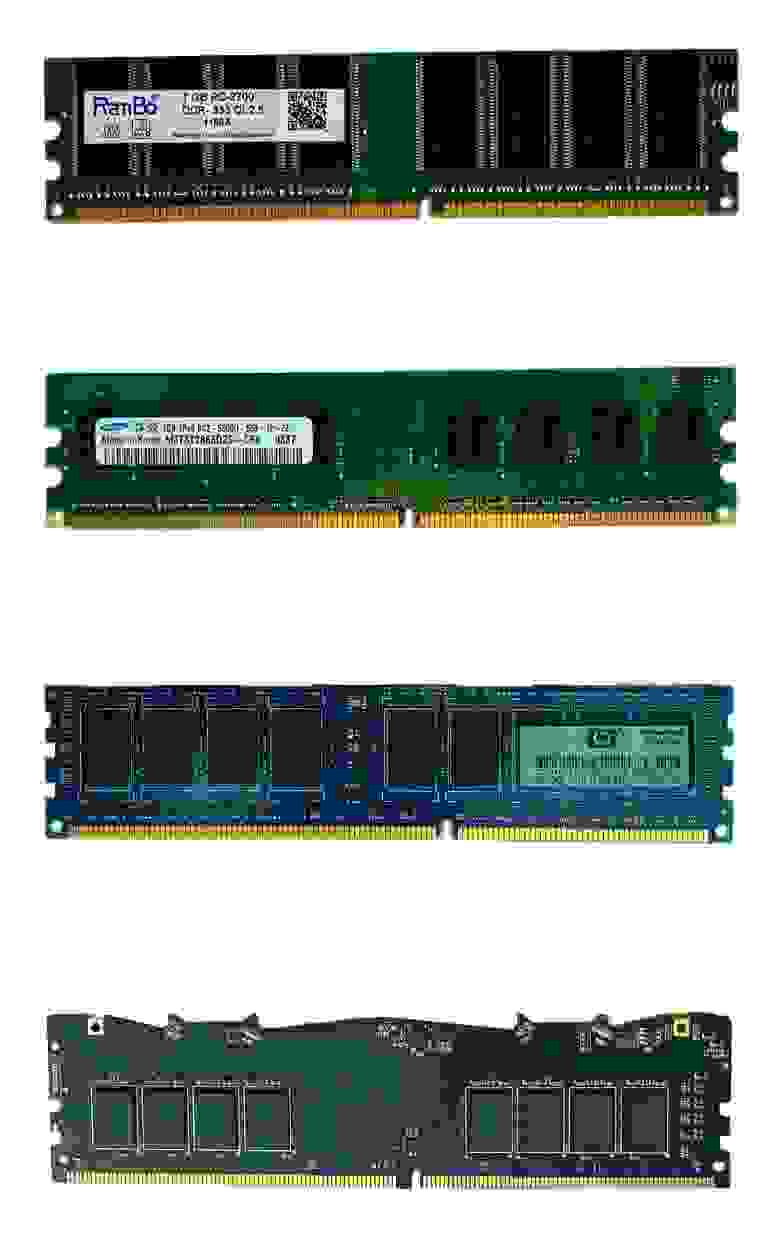

Сами DIMM имеют разный размер и количество чипов:

На фотографии сверху показана стандартная DIMM для настольного ПК, а под ней находится так называемая SO-DIMM (small outline, «DIMM малого профиля»). Маленький модуль предназначен для ПК малого форм-фактора, например, ноутбуков и компактных настольных компьютеров. Из-за малого пространства уменьшается количество используемых чипов, изменяется скорость работы памяти, и так далее.

Существует три основных причины для использования нескольких чипов памяти на DIMM:

То есть каждому DIMM, который устанавливается в компьютер с Ryzen, потребуется восемь модулей DRAM (8 чипов x 8 бит = 64 бита). Можно подумать, что графическая карта 5700 XT будет иметь 32 чипа памяти, но у неё их только 8. Что же это нам даёт?

В чипы памяти, предназначенные для графических карт, устанавливают больше банков, обычно 16 или 32, потому что для 3D-рендеринга необходим одновременный доступ к большому объёму данных.

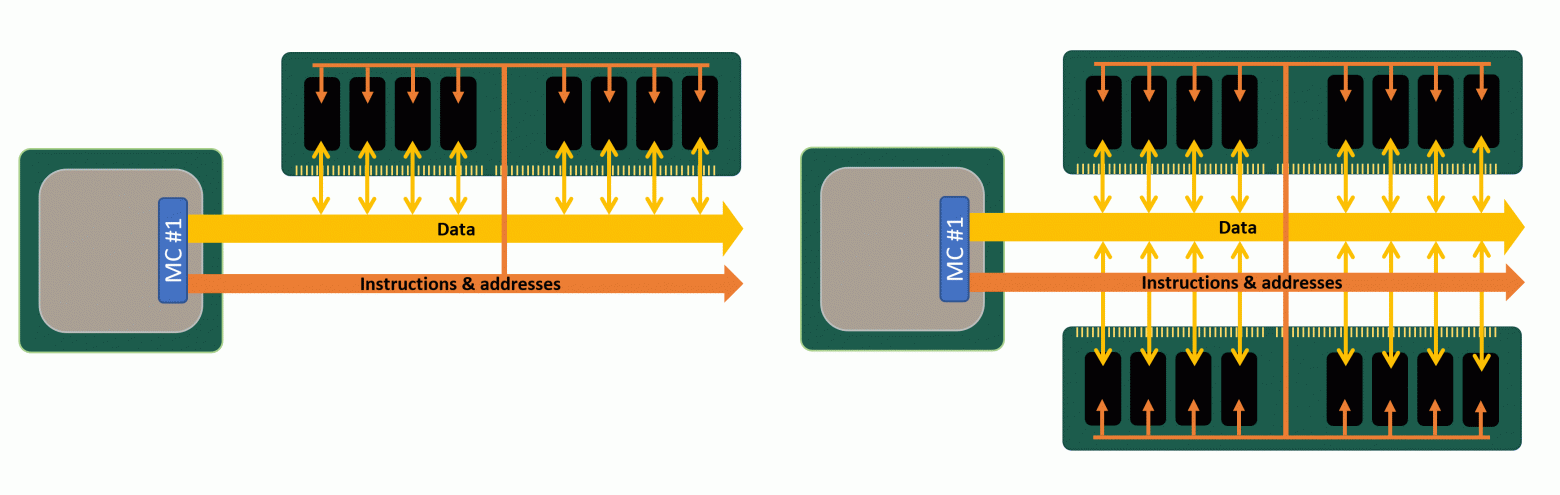

Один ранг и два ранга

Множество модулей памяти, «заполняющих» шину данных контроллера памяти, называется рангом, и хотя к контроллеру можно подключить больше одного ранга, за раз он может получать данные только от одного ранга (потому что ранги используют одну шину данных). Это не вызывает проблем, потому что пока один ранг занимается ответом на переданную ему команду, другому рангу можно передать новый набор команд.

Платы DIMM могут иметь несколько рангов и это особенно полезно, когда вам нужно огромное количество памяти, но на материнской плате мало разъёмов под RAM.

Так называемые схемы с двумя (dual) или четырьмя (quad) рангами потенциально могут обеспечить большую производительность, чем одноранговые, но увеличение количества рангов быстро повышает нагрузку на электрическую систему. Большинство настольных ПК способно справиться только с одним-двумя рангами на один контроллер. Если системе нужно больше рангов, то лучше использовать DIMM с буферизацией: такие платы имеют дополнительный чип, облегчающий нагрузку на систему благодаря хранению команд и данных в течение нескольких циклов, прежде чем передать их дальше.

Множество модулей памяти Nanya и один буферный чип — классическая серверная RAM

Но не все ранги имеют размер 64 бита — используемые в серверах и рабочих станциях DIMM часто размером 72 бита, то есть на них есть дополнительный модуль DRAM. Этот дополнительный чип не обеспечивает повышение объёма или производительности; он используется для проверки и устранения ошибок (error checking and correcting, ECC).

Вы ведь помните, что всем процессорам для работы нужна память? В случае ECC RAM небольшому устройству, выполняющему работу, предоставлен собственный модуль.

Шина данных в такой памяти всё равно имеют ширину всего 64 бита, но надёжность хранения данных значительно повышается. Использование буферов и ECC только незначительно влияет на общую производительность, зато сильно повышает стоимость.

Жажда скорости

У всех DRAM есть центральный тактовый сигнал ввода-вывода (I/O, input/output) — напряжение, постоянно переключающееся между двумя уровнями; он используется для упорядочивания всего, что выполняется в чипе и шинах памяти.

Если бы мы вернулись назад в 1993 год, то смогли бы приобрести память типа SDRAM (synchronous, синхронная DRAM), которая упорядочивала все процессы с помощью периода переключения тактового сигнала из низкого в высокое состояние. Так как это происходит очень быстро, такая система обеспечивает очень точный способ определения времени выполнения событий. В те времена SDRAM имела тактовые сигналы ввода-вывода, обычно работавшие с частотой от 66 до 133 МГц, и за каждый такт сигнала в DRAM можно было передать одну команду. В свою очередь, чип за тот же промежуток времени мог передать 8 бит данных.

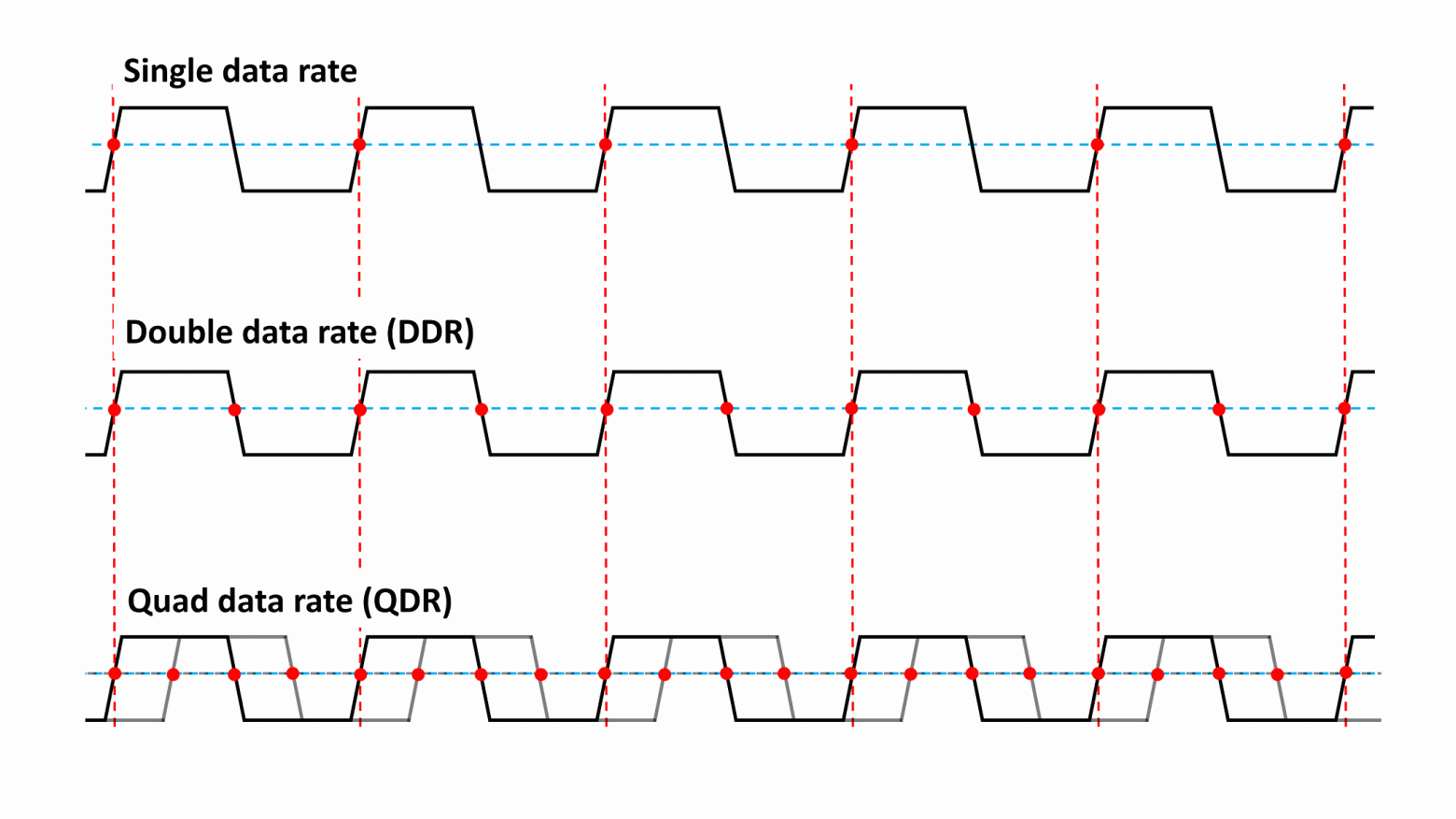

Быстрое развитие SDRAM, ведущей силой которого был Samsung, привело к созданию в 1998 году её нового типа. В нём передача данных синхронизировалась по повышению и падению напряжения тактового сигнала, то есть за каждый такт данные можно было дважды передать в DRAM и обратно.

Как же называлась эта восхитительная новая технология? Double data rate synchronous dynamic random access memory (синхронная динамическая память с произвольным доступом и удвоенной скоростью передачи данных). Обычно её просто называют DDR-SDRAM или для краткости DDR.

Память DDR быстро стала стандартом (из-за чего первоначальную версию SDRAM переименовали в single data rate SDRAM, SDR-DRAM) и в течение последующих 20 лет оставалась неотъемлемой частью всех компьютерных систем.

Прогресс технологий позволил усовершенствовать эту память, благодаря чему в 2003 году появилась DDR2, в 2007 году — DDR3, а в 2012 году — DDR4. Каждая новая версия обеспечивала повышение производительности благодаря ускорению тактового сигнала ввода-вывода, улучшению систем сигналов и снижению энергопотребления.

DDR2 внесла изменение, которое мы используем и сегодня: генератор тактовых сигналов ввода-вывода превратился в отдельную систему, время работы которой задавалось отдельным набором синхронизирующих сигналов, благодаря чему она стала в два раза быстрее. Это аналогично тому, как CPU используют для упорядочивания работы тактовый сигнал 100 МГц, хотя внутренние синхронизирующие сигналы работают в 30-40 раз быстрее.

DDR3 и DDR4 сделали шаг вперёд, увеличив скорость тактовых сигналов ввода-вывода в четыре раза, но во всех этих типах памяти шина данных для передачи/получения информации по-прежнему использовала только повышение и падение уровня сигнала ввода-вывода (т.е. удвоенную частоту передачи данных).

Сами чипы памяти не работают на огромных скоростях — на самом деле, они шевелятся довольно медленно. Частота передачи данных (измеряемая в миллионах передач в секунду — millions of transfers per second, MT/s) в современных DRAM настолько высока благодаря использованию в каждом чипе нескольких банков; если бы на каждый модуль приходился только один банк, всё работало бы чрезвычайно медленно.

| Тип DRAM | Обычная частота чипа | Тактовый сигнал ввода-вывода | Частота передачи данных |

| SDR | 100 МГц | 100 МГц | 100 MT/s |

| DDR | 100 МГц | 100 МГц | 200 MT/s |

| DDR2 | 200 МГц | 400 МГц | 800 MT/s |

| DDR3 | 200 МГц | 800 МГц | 1600 MT/s |

| DDR4 | 400 МГц | 1600 МГц | 3200 MT/s |

Каждая новая версия DRAM не обладает обратной совместимостью, то есть используемые для каждого типа DIMM имеют разные количества электрических контактов, разъёмы и вырезы, чтобы пользователь не мог вставить память DDR4 в разъём DDR-SDRAM.

Сверху вниз: DDR-SDRAM, DDR2, DDR3, DDR4

DRAM для графических плат изначально называлась SGRAM (synchronous graphics, синхронная графическая RAM). Этот тип RAM тоже подвергался усовершенствованиям, и сегодня его для понятности называют GDDR. Сейчас мы достигли версии 6, а для передачи данных используется система с учетверённой частотой, т.е. за тактовый цикл происходит 4 передачи.

| Тип DRAM | Обычная частота памяти | Тактовый сигнал ввода-вывода | Частота передачи данных |

| GDDR | 250 МГц | 250 МГц | 500 MT/s |

| GDDR2 | 500 МГц | 500 МГц | 1000 MT/s |

| GDDR3 | 800 МГц | 1600 МГц | 3200 MT/s |

| GDDR4 | 1000 МГц | 2000 МГц | 4000 MT/s |

| GDDR5 | 1500 МГц | 3000 МГц | 6000 MT/s |

| GDDR5X | 1250 МГц | 2500 МГц | 10000 MT/s |

| GDDR6 | 1750 МГц | 3500 МГц | 14000 MT/s |

Кроме более высокой частоты передачи, графическая DRAM обеспечивает дополнительные функции для ускорения передачи, например, возможность одновременного открытия двух страниц одного банка, работающие в DDR шины команд и адресов, а также чипы памяти с гораздо большими скоростями тактовых сигналов.

Какой же минус у всех этих продвинутых технологий? Стоимость и тепловыделение.

Один модуль GDDR6 примерно вдвое дороже аналогичного чипа DDR4, к тому же при полной скорости он становится довольно горячим — именно поэтому графическим картам с большим количеством сверхбыстрой RAM требуется активное охлаждение для защиты от перегрева чипов.

Скорость битов

Производительность DRAM обычно измеряется в количестве битов данных, передаваемых за секунду. Ранее в этой статье мы говорили, что используемая в качестве системной памяти DDR4 имеет чипы с 8-битной шириной шины, то есть каждый модуль может передавать до 8 бит за тактовый цикл.

То есть если частота передачи данных равна 3200 MT/s, то пиковый результат равен 3200 x 8 = 25 600 Мбит в секунду или чуть больше 3 ГБ/с. Так как большинство DIMM имеет 8 чипов, потенциально можно получить 25 ГБ/с. Для GDDR6 с 8 модулями этот результат был бы равен 440 ГБ/с!

Обычно это значение называют полосой пропускания (bandwidth) памяти; оно является важным фактором, влияющим на производительность RAM. Однако это теоретическая величина, потому что все операции внутри чипа DRAM не происходят одновременно.

Чтобы разобраться в этом, давайте взглянем на показанное ниже изображение. Это очень упрощённое (и нереалистичное) представление того, что происходит, когда данные запрашиваются из памяти.

На первом этапе активируется страница DRAM, в которой содержатся требуемые данные. Для этого памяти сначала сообщается, какой требуется ранг, затем соответствующий модуль, а затем конкретный банк.

Чипу передаётся местоположение страницы данных (адрес строки), и он отвечает на это передачей целой страницы. На всё это требуется время и, что более важно, время нужно и для полной активации строки, чтобы гарантировать полную блокировку строки битов перед выполнением доступа к ней.

Затем определяется соответствующий столбец и извлекается единственный бит информации. Все типы DRAM передают данные пакетами, упаковывая информацию в единый блок, и пакет в современной памяти почти всегда равен 8 битам. То есть даже если за один тактовый цикл извлекается один бит, эти данные нельзя передать, пока из других банков не будет получено ещё 7 битов.

А если следующий требуемый бит данных находится на другой странице, то перед активацией следующей необходимо закрыть текущую открытую страницу (это процесс называется pre-charging). Всё это, разумеется, требует больше времени.

Все эти различные периоды между временем отправки команды и выполнением требуемого действия называются таймингами памяти или задержками. Чем ниже значение, тем выше общая производительность, ведь мы тратим меньше времени на ожидание завершения операций.

Некоторые из этих задержек имеют знакомые фанатам компьютеров названия:

| Название тайминга | Описание | Обычное значение в DDR4 |

| tRCD | Row-to-Column Delay: количество циклов между активацией строки и возможностью выбора столбца | 17 циклов |

| CL | CAS Latency: количество циклов между адресацией столбца и началом передачи пакет данных | 15 циклов |

| tRAS | Row Cycle Time: наименьшее количество циклов, в течение которого строка должна оставаться активной перед тем, как можно будет выполнить её pre-charging | 35 циклов |

| tRP | Row Precharge time: минимальное количество циклов, необходимое между активациями разных строк | 17 циклов |

Существует ещё много других таймингов и все их нужно тщательно настраивать, чтобы DRAM работала стабильно и не искажала данные, имея при этом оптимальную производительность. Как можно увидеть из таблицы, схема, демонстрирующая циклы в действии, должна быть намного шире!

Хотя при выполнении процессов часто приходится ждать, команды можно помещать в очереди и передавать, даже если память занята чем-то другим. Именно поэтому можно увидеть много модулей RAM там, где нам нужна производительность (системная память CPU и чипы на графических картах), и гораздо меньше модулей там, где они не так важны (в жёстких дисках).

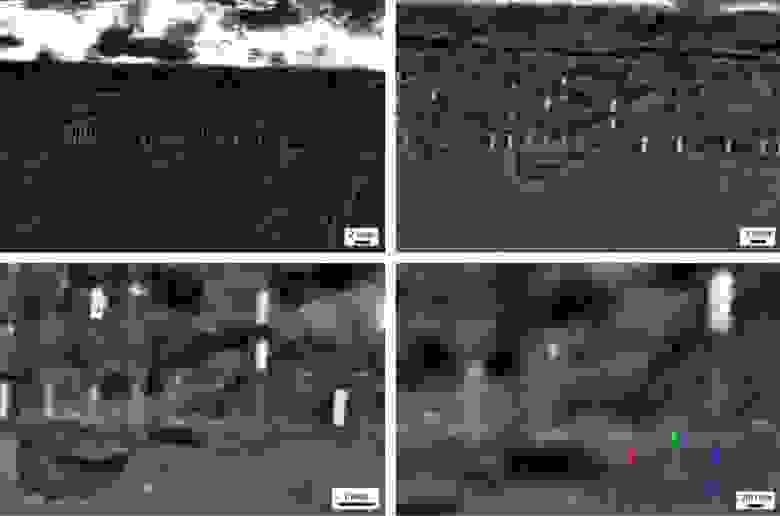

Тайминги памяти можно настраивать — они не заданы жёстко в самой DRAM, потому что все команды поступают из контроллера памяти в процессоре, который использует эту память. Производители тестируют каждый изготавливаемый чип и те из них, которые соответствуют определённым скоростям при заданном наборе таймингов, группируются вместе и устанавливаются в DIMM. Затем тайминги сохраняются в небольшой чип, располагаемый на плате.

Даже памяти нужна память. Красным указано ПЗУ (read-only memory, ROM), в котором содержится информация SPD.

Процесс доступа к этой информации и её использования называется serial presence detect (SPD). Это отраслевой стандарт, позволяющий BIOS материнской платы узнать, на какие тайминги должны быть настроены все процессы.

Многие материнские платы позволяют пользователям изменять эти тайминги самостоятельно или для улучшения производительности, или для повышения стабильности платформы, но многие модули DRAM также поддерживают стандарт Extreme Memory Profile (XMP) компании Intel. Это просто дополнительная информация, хранящаяся в памяти SPD, которая сообщает BIOS: «Я могу работать с вот с такими нестандартными таймингами». Поэтому вместо самостоятельной возни с параметрами пользователь может настроить их одним нажатием мыши.

Спасибо за службу, RAM!

В отличие от других уроков анатомии, этот оказался не таким уж грязным — DIMM сложно разобрать и для изучения модулей нужны специализированные инструменты. Но внутри них таятся потрясающие подробности.

Возьмите в руку планку памяти DDR4-SDRAM на 8 ГБ из любого нового ПК: в ней упаковано почти 70 миллиардов конденсаторов и такое же количество транзисторов. Каждый из них хранит крошечную долю электрического заряда, а доступ к ним можно получить за считанные наносекунды.

Даже при повседневном использовании она может выполнять бесчисленное количество команд, и большинство из плат способны без малейших проблем работать многие годы. И всё это меньше чем за 30 долларов? Это просто завораживает.

DRAM продолжает совершенствоваться — уже скоро появится DDR5, каждый модуль которой обещает достичь уровня полосы пропускания, с трудом достижимый для двух полных DIMM типа DDR4. Сразу после появления она будет очень дорогой, но для серверов и профессиональных рабочих станций такой скачок скорости окажется очень полезным.

Национальная библиотека им. Н. Э. Баумана

Bauman National Library

Персональные инструменты

RAM (Random Access Memory)

Содержание

История

В 1834 году Чарльз Бэббидж начал разработку аналитической машины. Одну из важных частей этой машины он называл «складом» (store), эта часть предназначалась для хранения промежуточных результатов вычислений. Информация в «складе» запоминалась в чисто механическом устройстве в виде поворотов валов и шестерней. ЭВМ первого поколения можно считать ещё полуэкспериментальными, поэтому в них использовалось множество разновидностей и конструкций запоминающих устройств, основанных на различных физических принципах:

Второе поколение требовало более технологичных, дешёвых и быстродействующих ОЗУ. Наиболее распространённым видом ОЗУ в то время стала память на магнитных сердечниках.

Начиная с третьего поколения большинство электронных узлов компьютеров стали выполнять на микросхемах, в том числе и ОЗУ. Наибольшее распространение получили два вида ОЗУ:

Статическая и динамическая память не сохраняли информацию при отключении питания. Сохранять информацию при отключении питания способна энергонезависимая память.

Ячейка памяти

Ячейка памяти это фундаментальный элемент в структуре модуля памяти компьютера. Ячейка памяти представляет собой электронную схему, которая хранит один бит двоичной информации:

Оперативное запоминающее устройство,

ОЗУ может изготавливаться как отдельный внешний модуль или располагаться на одном кристалле с процессором, например, в однокристальных ЭВМ или однокристальных микроконтроллерах.

Основные типы RAM